# Principles of Transistor Circuits EIGHTH EDITION

INTRODUCTION TO THE DESIGN OF AMPLIFIERS, RECEIVERS AND DIGITAL CIRCUITS

SW AMOS, BSc, CENG, MIEE

formerly Head of Technical Publications Section, Engineering Training Department, British Broadcasting Corporation

Newnes An imprint of Butterworth-Heinemann Linacre House, Jordan Hill, Oxford OX2 8DP 225 Wildwood Avenue, Woburn, MA 01801-2041 A division of Reed Educational and Professional Publishing Ltd

- A member of the Reed Elsevier plc group

OXFORD BOSTON JOHANNESBURG MELBOURNE NEW DELHI SINGAPORE

First published by Iliffe Books Ltd 1959 Second edition 1961 Third edition 1965 Fourth edition 1969 Fifth edition 1975 Sixth edition 1981 Seventh edition 1990 Eighth edition 1994 Reprinted 1995, 1997, 1998

© S. W. Amos 1994

All rights reserved. No part of this publication may be reproduced in any aterial form (including photocopying or storing in any medium by electronic means and whether or not transiently or incidentally to some other use of this publication) without the written permission of the copyright holder except in accordance with the provisions of the Copyright, Designs and Patents Act 1988 or under the terms of a licence issued by the Copyright Licensing Agency Ltd, 90 Tottenham Court Road, London, England W1P 9HE. Application for the copyright holder's written permission to reproduce any part of this publication should be addressed to the publishers

British Library Cataloguing in Publication Data

Amos, S. W.

Principles of transistor circuits. - 8th ed.

1. Transistor circuits

2. Electronic circuit design

1. Title

621.3815'30455 TK7871.9

ISBN 0 7506 1999 6

#### Library of Congress Cataloguing in Publication Data

Amos, S. W. (Stanley William)

Principles of transistor circuits/S. W. Amos. - 8th ed.

p. cm.

ISBN 0 7506 1999 6

1. Transistor circuits. I. Title

TK7871.9A45 1994

621.381'528---dc20 93-50682

Printed and bound in Great Britain

### Preface to the Eighth Edition

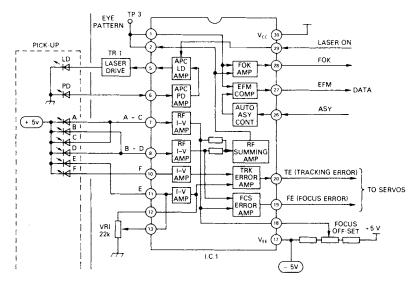

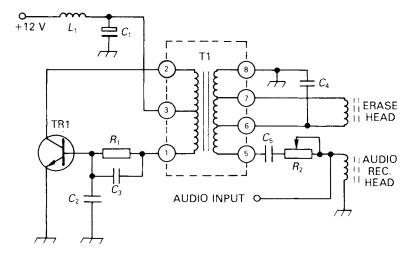

The principal changes introduced in this new edition were made to keep the book abreast of progress in electronics. To this end material has been added on new components such as h.e.m.t.s and to illustrate the use of transistors in modern equipment such as camcorders, video recorders, CD players and satellite receivers.

The preparation of this edition was undertaken by the author's friend and colleague Eugene Trundle, who selected the new material and wrote the associated text. He also made minor rearrangements of chapter contents to improve the clarity of presentation. The author gratefully acknowledges this help.

> S. W. Amos, Broadway, September 1993

# Semiconductors and Junction Diodes

#### INTRODUCTION

The 1950s marked the beginning of a revolution in electronics. It started with the invention by William Shockley of the transistor, a minute three-terminal device which could switch, amplify and oscillate yet needed only a few microwatts of power; it was also robust and virtually everlasting. Inevitably the transistor replaced the electron tube (valve) in all except very high power applications.

The pace of the revolution was accelerated a decade later by the development of the integrated circuit or i.c. (popularly known as the silicon chip) in which transistors and other components are manufactured and interconnected by the planar process (see Appendix A) to form amplifiers, signal stores and other functional units on a single silicon slice. The miniaturisation now possible is such that several million transistors can be accommodated on an i.c. less than  $1 \text{ cm}^2$ .

The applications of i.c.s seem boundless. They feature in activities as diverse as satellite communication and control of model railways. They are widely used in audio, video and radio equipment and they made possible the computers and microprocessors now universally employed in commerce and industry. Perhaps their most familiar applications are in digital watches, calculators and toys.

This book describes the properties of the various types of transistor and shows how they can be used in the design of electronic circuits. The principles described apply to circuits employing discrete transistors and those embodied in i.c.s. To explain the properties of transistors it is useful to begin with an account of the physics of semiconductors because all transistors, irrespective of type, depend on semiconducting material for their action.

#### MECHANISM OF SEMICONDUCTION

As the name suggests a semiconducting material is one with a conductivity lying between that of an insulator and that of a conductor: that is to say one for which the resistivity lies between, say  $10^{12} \Omega$ -cm (a value typical of glass) and  $10^{-6} \Omega$ -cm (approximately the value for copper). Typical values for the resistivity of a semiconducting material lie between 1 and  $100 \Omega$ -cm.

Such a value of resistivity could, of course, be obtained by mixing a conductor and an insulator in suitable proportions but the resulting material would not be a semiconductor. Another essential feature of a semiconducting material is that its electrical resistance

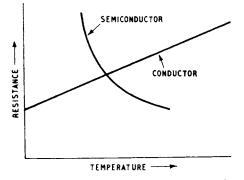

Fig. 1.1. Resistance-temperature relationship for a conductor and a semiconductor

decreases with increase in temperature over a particular temperature range which is characteristic of the semiconductor. This behaviour contrasts with that of elemental metallic conductors for which the resistance increases with rise in temperature. This is illustrated in Fig. 1.1, which gives curves for a conductor and a semiconductor. The resistance of the conductor increases linearly, whereas that of the semiconductor decreases exponentially, as temperature rises. Over the significant temperature range the between resistance and temperature for а relationship semiconductor could be written

$$R_i = ae^{b T}$$

where  $R_i$  is the resistance at an absolute temperature T, a and b are constants characteristic of the semiconductor material and e is the

base of the natural logarithms, i.e. 2.81828... The two curves in Fig. 1.1 are not to the same vertical scale of resistance.

All semiconducting materials exhibit the temperature dependence discussed in the paragraphs above in the pure state: the addition of impurities raises the temperature at which the material exhibits this behaviour, i.e. the region of negative temperature coefficient.

The element most widely used in transistor manufacture is silicon. It has largely replaced germanium which was also used in early transistors. When pure both elements have very poor conductivity and are of little direct use in transistor manufacture. But by the addition of a very small but controlled quantity of a particular type of impurity the conductivity can be increased and the material made suitable for use in transistors.

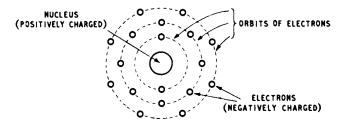

The behaviour of semiconductors can be explained in terms of atomic theory. The atom is assumed to have a central nucleus which carries most of the mass of the atom and has a positive charge. A number of electrons carrying a negative charge revolve around the nucleus. The total number of electrons revolving around a

Fig. 1.2. Simplified diagram of structure of atom: for simplicity, electron orbits are shown as circular and co-planar

particular nucleus is sufficient to offset the positive nuclear charge, leaving the atom electrically neutral. The number of electrons associated with a given nucleus is equal to the atomic number of the element. The electrons revolve in a number of orbits and, for the purpose of this discussion, the orbits may be regarded as concentric, the nucleus being at the centre, as shown in Fig. 1.2. This diagram is greatly simplified; the orbits are in practice neither concentric nor co-planar.

The first orbit (sometimes called a ring or a shell) is complete when it contains 2 electrons, and an atom with a single complete shell is that of the inert gas, helium. The second ring is complete when it has 8 electrons, and the atom with the first 2 rings complete is that of the inert gas, neon. The third ring is stable when it has 8 or 18 electrons, and the atom having 2, 8 and 8 electrons in the 1st, 2nd and 3rd rings is that of the inert gas, argon. All the inert gases have their outermost shells stable. It is difficult to remove any electrons from a stable ring or to insert others into it. Atoms combine by virtue of the electrons in the outermost rings: for example an atom with one electron in the outermost ring will willingly combine with another whose outermost ring requires one electron for completion.

The inert gases, having their outer shells stable, cannot combine with other atoms or with each other. The number of electrons in the outermost ring or the number of electrons required to make the outermost ring complete has a bearing on the chemical valency of the element and the outermost ring is often called the *valence ring*.

Now consider the copper atom: it has 4 rings of electrons, the first 3 being complete and the 4th containing 1 electron, compared with the 32 needed for completion. Similarly the silver atom has 5 rings, 4 stable and the 5th also containing 1 out of 50 needed for completion. The atoms of both elements thus contain a single electron and this is loosely bound to the nucleus. It can be removed with little effort and is termed a *free electron*. A small e.m.f. applied to a collection of these atoms can set up a stream of free electrons, i.e. an electric current through the metal. Elements in which such free electrons are available are good electrical conductors.

It might be thought that an atom with 17 electrons in the outermost orbit would be an even better conductor, but this is not so. If one electron is added to such an orbit it becomes complete and a great effort is needed to remove it again.

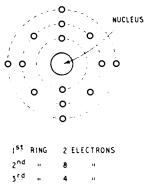

The arrangement of orbital electrons in a silicon atom is pictured in Fig. 1.3. There are three rings, the first containing 2 electrons, the

second 8 and the third 4. The total number of electrons is 14, the atomic number of silicon. For comparison the germanium atom has four rings containing 2, 8, 18 and 4 electrons. These total 32, the atomic number for germanium. A significant feature of both atomic structures is that the outermost ring contains 4 electrons, a property of elements belonging to Group IV of the Periodic Table.

#### Covalent Bonds

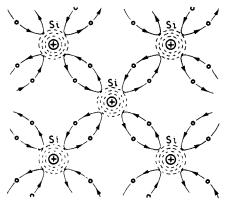

It might be thought that some of the 4 electrons in the valence ring of the silicon atom could easily be displaced and that these elements would therefore be good conductors. In fact, crystals of pure silicon are very poor conductors. To understand this we must consider the relationships between the valence electrons of neighbouring atoms when these are arranged in a regular geometric pattern as in a crystal. The valence electrons of each atom form bonds, termed *covalent bonds*, with those of neighbouring atoms as suggested in Fig. 1.4. It is difficult to portray a three-dimensional phenomenon in a twodimensional diagram, but the diagram does show the valence electrons oscillating between two neighbouring atoms. The atoms behave in some respects as though each outer ring had 8 electrons and was stable. There are no free electrons and such a crystal is therefore an insulator: this is true of pure silicon at a very low temperature.

At room temperatures, however, silicon crystals do have a small conductivity even when they are as pure as modern chemical methods can make them. This is partly due to the presence of minute traces of

Fig 1.4. Illustrating covalent bonds in a crystal of pure silicon: for simplicity only electrons in the valence rings are shown

impurities (the way in which these increase conductivity is explained later) and partly because thermal agitation enables some valence electrons to escape from their covalent bonds and thus become available as charge carriers. They are able to do this by virtue of their kinetic energy which, at normal temperatures, is sufficient to allow a very small number to break these bonds. If their kinetic energy is increased by the addition of light or by increase in temperature, more valence electrons escape and the conductivity increases. If the temperature is raised sufficiently conductivity becomes so great that it swamps semiconductor behaviour. This sets an upper limit to the temperature at which semiconductor devices can operate normally. For silicon devices the limit is sometimes quoted as 150°C.

#### **Donor Impurities**

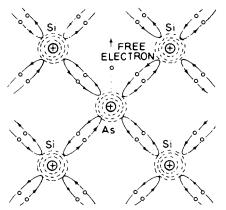

Suppose an atom of a Group-V element such as arsenic is introduced into a crystal of pure silicon. The atom enters into the lattice structure, taking the place of a silicon atom. Now the arsenic atom has 5 electrons in its outermost orbit and 4 of these form covalent bonds with the electrons of neighbouring atoms as shown in Fig. 1.5. The remaining (5th) electron is left unattached; it is a free electron which can be made to move through the crystal by an e.m.f., leaving a positively charged ion. These added electrons give the crystal much better conductivity than pure silicon and the

Fig. 1.5. Illustrating covalent bonds in the neighbourhood of an atom of a Group-V element introduced into a crystal of pure silicon. For simplicity only electrons in the valence rings are shown

added element is termed a *donor* because it gives free electrons to the crystal. Silicon so treated with a Group-V element is termed *n-type* because negatively charged particles are available to carry charge through the crystal. It is significant that the addition of the arsenic or some other Group-V element was necessary to give this improvement in conductivity. The added element is often called an impurity and in the language of the chemist it undoubtedly is. However, the word is unfortunate in this context because it suggests that the pentavalent element is unwanted; in fact, it is essential.

When a battery is connected across a crystal of n-type semiconductor the free electrons are attracted towards the battery positive terminal and repelled from the negative terminal. These forces cause a drift of electrons through the crystal from the negative to the positive terminal: for every electron leaving the crystal to enter the positive terminal another must be liberated from the negative terminal to enter the crystal. The stream of electrons through the crystal constitutes an electric current. If the voltage applied to the crystal is varied the current varies also in direct proportion, and if the battery connections are reversed the direction of the current through the crystal also reverses but it does not change in amplitude; that is to say the crystal is a *linear* conductor.

#### Acceptor Impurities

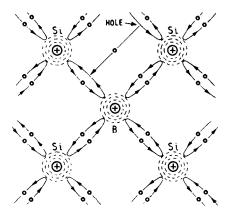

Now suppose an atom of a Group-III element such as boron is introduced into a crystal of pure silicon. It enters the lattice structure, taking the place of a silicon atom, and the 3 electrons in the valence ring of the boron atom form covalent bonds with the valence electrons of the neighbouring silicon atoms. To make up the number of covalent bonds to 4, each boron atom competes with a neighbouring atom and may leave this deficient of one electron as shown in Fig. 1.6. A group of covalent bonds, which is deficient of one electron, behaves in much the same way as a positively charged particle with a charge equal in magnitude to that of an electron. Such a particle is called a hole in semiconductor theory, and we may say that the introduction of the Group-III impurity gives rise to holes in a crystal of pure silicon. These can carry charge through the crystal and, because these charge carriers have a positive sign, silicon treated with a Group-III impurity is termed p-type. Such an impurity is termed an acceptor impurity because it takes electrons from the silicon atoms. Thus the introduction of the Group-III element into a crystal lattice of pure silicon also

8

Fig. 1.6. Illustrating covalent bonds in the neighbourhood of an atom of a Group-III element, introduced into a crystal of pure silicon. For simplicity, only electrons in the valence rings are shown

increases the conductivity considerably and, when a battery is connected across a crystal of p-type silicon, a current can flow through it in the following manner.

The holes have an effective positive charge, and are therefore attracted towards the negative terminal of the battery and repulsed by the positive terminal. They therefore drift through the crystal from the positive to the negative terminal. Each time a hole reaches the negative terminal, an electron is emitted from this terminal into the hole in the crystal to neutralise it. At the same time an electron from a covalent bond enters the positive terminal to leave another hole in the crystal. This immediately moves towards the negative terminal, and thus a stream of holes flows through the crystal from the positive to the negative terminal. The battery thus loses a steady stream of electrons from the negative terminal and receives a similar stream at its positive terminal. It may be said that a stream of electrons has passed through the crystal from the negative to the positive terminal. A flow of holes is thus equivalent to a flow of electrons in the opposite direction.

If the battery voltage is varied the current also varies in direct proportion: thus p-type silicon is also a linear conductor.

It is astonishing how small the impurity concentration must be to make silicon suitable for use in transistors. A concentration of 1 part in  $10^6$  may be too large, and concentrations commonly used are of a few parts in  $10^8$ . A concentration of 1 part in  $10^8$ increases the conductivity by 16 times. Before such a concentration can be introduced, the silicon must first be purified to such an extent that any impurities still remaining represent concentrations very much less than this. Purification is one of the most difficult processes in the manufacture of transistors. The addition of the impurity is commonly termed *doping*.

#### Intrinsic and Extrinsic Semiconductor

If a semiconductor crystal contains no impurities, the only charge carriers present are those produced by thermal breakdown of the covalent bonds. The conducting properties are thus characteristic of the pure semiconductor. Such a crystal is termed an *intrinsic* semiconductor.

In general, however, the semiconductor crystals contain some Group-III and some Group-V impurities, i.e. some donors and some acceptors. Some free electrons fit into some holes and neutralise them but there are some residual charge carriers left. If these are mainly electrons they are termed *majority carriers* (the holes being *minority carriers*), and the material is n-type. If the residual charge carriers are mainly holes, these are majority carriers (the electrons being minority carriers) and the semiconductor is termed p-type. In an n-type or p-type crystal the impurities are chiefly responsible for the conduction, and the material is termed an *extrinsic* semiconductor.

#### COMPOUND SEMICONDUCTORS

In a silicon crystal covalent bonds between the valence electrons of neighbouring atoms cause the atoms to behave as though the outermost electron orbits were complete. The crystal is therefore effectively a non-conductor until an impurity is introduced. A similar process can occur in a compound of a trivalent and a pentavalent element. Here, too, sharing of the valence electrons yields an effectively complete outer shell and the resulting insulating property can again be destroyed by the introduction of a suitable impurity.

There are a number of such compound semiconductors (known as III-V compounds from the columns of the Periodic Table) but the most widely used is gallium arsenide, GaAs. This has a number of advantages over silicon. For example, the mobility of electrons in GaAs is five times that in silicon, making GaAs transistors suitable for use at microwave frequencies and in computers where high-speed switching is required. Moreover intrinsic GaAs is a better insulator than silicon which helps in the manufacture of integrated circuits. Thirdly GaAs retains its semiconducting properties up to a higher temperature. GaAs is widely used in the manufacture of light-emitting diodes.

Other compound semiconductors contain divalent and hexavalent elements. An example of a II-VI compound is cadmium sulphide CdS.

#### **PN JUNCTIONS**

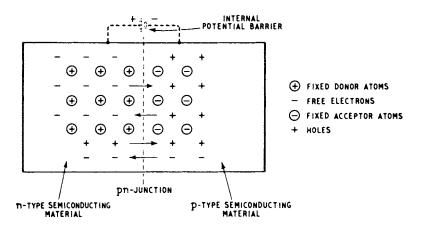

As already mentioned, an n-type or p-type semiconductor is a linear conductor, but if a crystal of semiconductor has n-type conductivity at one end and p-type at the other end, as indicated in Fig. 1.7, the crystal so produced has asymmetrical conducting properties. That is to say, the current which flows in the crystal when an e.m.f. is applied between the ends depends on the polarity of the e.m.f., being small when the e.m.f. is in one direction and large when it is reversed. Crystals with such conductive properties have obvious applications as detectors or rectifiers.

It is not possible, however, to produce a structure of this type by placing a crystal of n-type semiconductor in contact with a crystal

Fig. 1.7. Pattern of fixed and mobile charges in the region of a pn junction

of p-type semiconductor. No matter how well the surfaces to be placed together are planed, or how perfect the contact between the two appears, the asymmetrical conductive properties are not properly obtained. The usual way of achieving a structure of this type is by treating one end of a single crystal of n-type semiconductor

11

with a Group-III impurity so as to offset the n-type conductivity at this end and to produce p-type conductivity instead at this point. Alternatively, of course, one end of a p-type crystal could be treated with a Group-V impurity to give n-type conductivity at this end. The semiconducting device so obtained is termed a *junction diode*, and the non-linear conducting properties can be explained in the following way.

#### Behaviour of a pn Junction

Fig. 1.7 represents the pattern of charges in a crystal containing a pn junction. The ringed signs represent charges due to the impurity atoms and are fixed in position in the crystal lattice: the unringed signs represent the charges of the free electrons and holes (majority carriers) which are liberated by the impurities. The n-region also contains a few holes and the p-region also a few free electrons: these are minority carriers which are liberated by thermal dissociation of the covalent bonds of the semiconducting element itself.

Even when no external connections are made to the crystal, there is a tendency, due to diffusion, for the free electrons of the n-region to cross the junction into the p-region: similarly the holes in the p-region tend to diffuse into the n-region. However, the moment any of these majority carriers cross the junction, the electrical neutrality of the two regions is upset: the n-region loses electrons and gains holes, both causing it to become positively charged with respect to the p-region. Thus a potential difference is established across the junction and this discourages further majority carriers from crossing the junction: indeed only the few majority carriers with sufficient energy succeed in crossing. The potential difference is, however, in the right direction to encourage minority carriers to cross the junction and these cross readily in just sufficient numbers to balance the subsequent small flow of majority carriers. Thus the balance of charge is preserved even though the crystal has a potential barrier across the junction. In Fig. 1.7 the internal potential barrier is represented as an external battery and is shown in dashed lines.

The potential barrier tends to establish a carrier-free zone, known as a *depletion urea*, at the junction. The depletion area is similar to the dielectric in a charged capacitor.

#### **Reverse-bias** Conditions

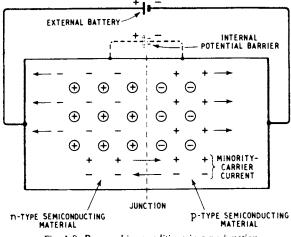

Suppose now an external battery is connected across the junction, the negative terminal being connected to the p-region and the

Fig. 1.8. Reverse-bias conditions in a pn junction

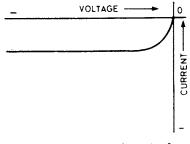

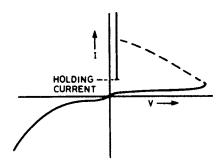

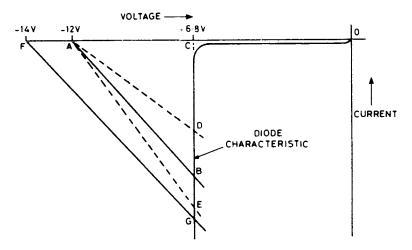

positive terminal to the n-region as shown in Fig. 1.8. This connection gives a *reverse-biased* junction. The external battery is in parallel with and aiding the fictitious battery, increasing the potential barrier across the junction and the width of the depletion area. Even the majority carriers with the greatest energy now find it almost impossible to cross the junction. On the other hand the minority carriers can cross the junction as easily as before and a steady stream of these flows across. When the minority carriers cross the junction they are attracted to the battery terminals and can then flow as a normal electric current in a conductor. Thus a current, carried by the minority carriers and known as the *reverse current*, flows across the junction. It is a small current because the number of minority carriers is small: it increases as the battery voltage is increased as shown in Fig. 1.9 but at a reverse voltage

Fig. 1.9. Current-voltage relationship for a reverse-biased pn junction

of less than 1 V becomes constant: this is the voltage at which the rate of flow of minority carriers becomes equal to the rate of production of carriers by thermal breakdown of covalent bonds. Increase in the temperature of the crystal produces more minority carriers and an increase in reverse current. A significant feature of the reverse-biased junction is that the width of the depletion area is controlled by the reverse bias, increasing as the bias increases.

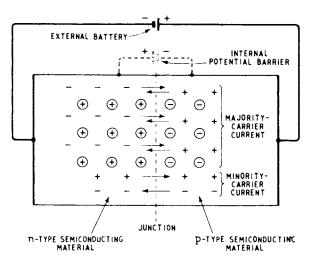

#### Forward-bias Conditions

If the external battery is connected as shown in Fig. 1.10 with the positive terminal connected to the p-region and the negative terminal to the n-region, the junction is said to be *forward-biased*. The external battery now opposes and reduces the potential barrier

Fig. 1.10. Forward-bias conditions in a pn junction

due to the fictitious battery and the majority carriers are now able to cross the junction more readily. The depletion area has now disappeared. Some of the holes and electrons recombine in the junction area so that the current flowing through the device (which can be very large) is carried by holes in the p-region and electrons in the n-region. If the semiconductor regions are equally doped the number of holes is equal to the number of electrons but the contribution to the forward current made by the holes and electrons depends on the degree of doping of the p- and n-regions. For example, if the doping of the p-region is much heavier than that of the n-region, the forward current will be carried mostly by holes.

The flow of minority carriers across the junction also continues as in reverse-bias conditions but at a reduced scale and these give rise to a second current also taken from the battery but in the opposite direction to that carried by the majority carriers. Except for very small external battery voltages, however, the minoritycarrier current is very small compared with the majority-carrier current and can normally be neglected in comparison with it.

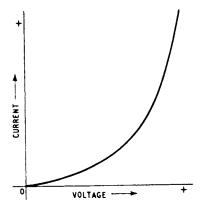

The relationship between current and forward-bias voltage is illustrated in Fig. 1.11. The curve has a small slope for small voltages because the internal potential barrier discourages movements of majority carriers across the junction. Increase in applied voltage tends to offset the internal barrier and current increases at a greater

Fig. 1.11. Current-voltage relationship for a forward-biased pn junction

rate. Further increase in voltage almost completely offsets the barrier and gives a steeply-rising current. The curve is, in fact, closely exponential in form.

A pn junction thus has asymmetrical conducting properties, allowing current to pass freely in one direction but hardly at all in the reverse direction.

#### JUNCTION DIODES

Small-signal diodes, i.e. those used for detection, mixing and switching, require a small junction area to minimise capacitance and

are usually encapsulated in a cylindrical glass or plastic envelope with coaxial leads which are soldered directly into circuit. Germanium was used in the 1950s and the diodes were manufactured by the alloy-junction process described in Appendix A but this was later superseded by a process using diffusion. Silicon junction diodes manufactured by the planar process were introduced in the 1960s. Germanium diodes have a much greater reverse current than silicon but conduction occurs at a lower forward voltage (0.2 V) compared with 0.7 V for silicon and they are preferred to silicon where this smaller voltage drop is important.

In rectifier diodes used for the production of d.c. supplies from a.c. sources the junction area must be large enough to carry the output current required and the chief problems are minimising the rise in junction temperature (a heat sink may be necessary to limit this) and the prevention of breakdown under the stress of the peak inverse voltage. Mains-voltage types are capable of handling currents of tens of amperes.

#### **Recovery Time**

When a conventional pn diode is forward biased some of the majority carriers crossing the junction are neutralised by combination with majority carriers of opposite polarity. Others remain (as minority carriers) and, when the applied voltage is reversed, return across the junction in the form of a substantial pulse of reverse current which takes a significant time to decay to the normal value of reverse current. This delay is a serious disadvantage in diodes required for operation at microwave frequencies or in high-speed switching.

#### Schottky Diode ('Hot-carrier' or 'Hot-electron' Diode)

A diode which overcomes this recovery-time difficulty is the Schottky diode which uses a metal-semiconductor contact instead of a pn junction. For example, in one form of construction a region of epitaxial\* n-type GaAs is grown on a GaAs substrate and a metallic layer is deposited on this. Ohmic connections are made to the substrate and the metallic layer. Only one type of charge carrier is involved in operation of the diode. When the 'metal is biased positively electrons from the n-region are attracted to it to neutralise the charge so giving rise to the forward current. When the metal is

\*See Appendix A. p. 368

negatively charged electrons are repelled and there is no reverse current. There is no p-layer in which electrons could be stored and the resulting diode is highly efficient at frequencies as high as 20 GHz.

#### Avalanche Effect

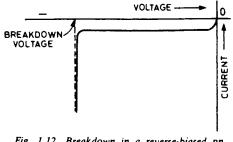

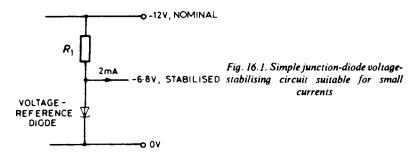

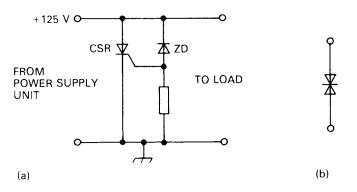

When a pn junction is reverse-biased the current is carried solely by the minority carriers, and at a given temperature the number of minority carriers is fixed. Ideally, therefore, we would expect the reverse current for a pn junction to rise to a saturation value as the voltage is increased from zero and then to remain constant and independent of voltage, as shown in Fig. 1.9. In practice, when the reverse voltage reaches a particular value which can be 100 V or more the reverse current increases very sharply as shown in Fig. 1.12, an effect known as breakdown. The effect is reproducible, breakdown in a particular junction always occurring at the same value of reverse voltage. This is known as the Avalanche effect and reversed-biased diodes known as Avalanche diodes (sometimes called-perhaps incorrectly-Zener diodes) can be used as the basis of a voltage stabiliser circuit. The junction diodes used for this purpose are usually silicon types and examples of voltage stabilising circuits employing such diodes are given in Chapter 16.

Fig. 1.12. Breakdown in a reverse-biased pn junction

The explanation of the Avalanche effect is thought to be as follows. The reverse voltage applied to a junction diode establishes an electric field across the junction and minority electrons entering it from the p-region are accelerated to the n-region as illustrated in Fig. 1.8. When this field exceeds a certain value some of these electrons collide with valence electrons of the atoms fixed in the crystal lattice and liberate them, thus creating further hole-electron pairs. Some new carriers are themselves accelerated by the electric field due to the reverse bias and in turn collide with other atoms, liberating still further holes and electrons. In this way the number of charge carriers increases very rapidly: the process is, in fact, regenerative. This multiplication in the number of charge carriers produces the sharp increase in reverse current shown in Fig. 1.12. Once the breakdown voltage is exceeded, a very large reverse current can flow and unless precautions are taken to limit this current the junction can be damaged by the heat generated in it. Voltage stabilising circuits using Avalanche diodes must therefore include protective measures to avoid damage due to this cause.

#### Capacitance Diode (Varactor Diode)

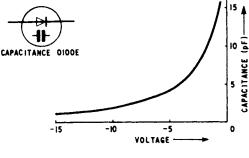

As pointed out above, the application of reverse bias to a pn junction discourages majority carriers from crossing the junction, and produces a depletion area, the width of which can be controlled by the magnitude of the reverse bias. Such a structure is similar to that of a charged capacitor and, in fact, a reverse-biased junction diode has the nature of a capacitance shunted by a high resistance. The value

Fig. 1.13. Symbol and typical capacitancevoltage characteristic for a capacitance diode

of the capacitance is dependent on the reverse-bias voltage and can be varied over wide limits by alteration in the bias voltage. This is illustrated in the curve of Fig. 1.13: the capacitance is inversely proportional to the applied voltage. A voltage-sensitive capacitance such as this has a number of useful applications: it can be used as a

#### 18 Principles of Transistor Circuits

frequency modulator, as a means of remote tuning in receivers or for automatic frequency control (a.f.c.) purposes in receivers. An example of one of these applications of the reverse-biased junction diode is given in Chapter 16.

#### Zener Effect

Some reverse-biased junction diodes exhibit breakdown at a very low voltage, say below 5 V. In such examples breakdown is thought to be due, not to Avalanche effect, but to Zener effect which does not involve ionisation by collision. Zener breakdown is attributed to spontaneous generation of hole-electron pairs within the junction region from the inner electron shells. Normally this region is carrierfree but the intense field established across the region by the reverse bias can produce carriers which are then accelerated away from the junction by the field, so producing a reverse current. The graphical symbol for a Zener diode is given in Fig. 1.14.

Fig. 1.14. Graphical symbol for a Zener diode

#### Voltage Reference Diode

The breakdown voltage of a reverse-biased junction diode can be placed within the range of a few volts to several hundred volts but for stabiliser and voltage reference applications it is unusual to employ a diode with a breakdown voltage exceeding a few tens of volts. Some of the reasons for this are given below.

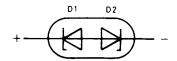

The breakdown voltage varies with temperature, the coefficient of variation being negative for diodes with breakdown voltages less than approximately 5.3 V and positive for diodes with breakdown voltages exceeding approximately 6.0 V. Diodes with breakdown voltages between these two limits have very small coefficients of variation and are thus well suited for use in voltage stabilisers. However, for voltage reference purposes, the slope resistance of the breakdown characteristic must be very small and the slope resistance is less for diodes with breakdown voltages. Where variations in temperature are likely to occur it is probably best to use a diode with a breakdown voltage between 5.3 and 6.0 V for voltage reference purposes but if means are available for stabilising the temperature it is probably better to use a diode with a higher breakdown voltage to obtain a lower slope resistance. Diodes with breakdown voltages around 6.8 V have a temperature coefficient (2.5 mV/°C) which matches that of forward-biased diodes. Voltage reference diodes therefore often consist of two Zener diodes connected in series back-to-back as shown in Fig. 1.15. D1 is reverse-biased when voltage

Fig. 1.15. Construction of a voltage reference diode

is applied and this has a positive temperature coefficient. D2 is forward-biased and has an equal negative temperature coefficient. The voltage across D2 is small compared with that across D1 and thus the voltage across the device is substantially the Zener voltage of D1 but independent of temperature.

Voltage reference diodes are usually marketed with preferred values of breakdown voltage (4.7, 5.6, 6.8 V, etc.) and with tolerances of 5 per cent or 10 per cent.

Early voltage reference diodes were rated for only 30 mW dissipation but modern types can withstand a pulse power up to 2.5 kW for a duration of 1 ms provided the pulse is not repetitive. Large diodes are used to protect radars, communications systems and delicate instruments from large electrical transients from nearby electrical equipment.

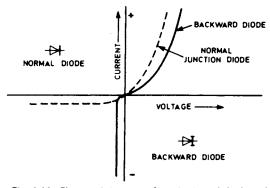

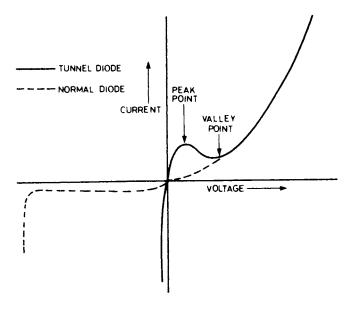

#### Backward Diode

If the breakdown voltage of a germanium diode is made very low, the region of low slope resistance virtually begins at the origin. Such a junction has a reverse resistance lower than the forward resistance and can be used as a diode which, by contrast with normal diodes, has low resistance when the p-region is biased negatively relative to the n-region. Such backward diodes, manufactured with low capacitance, make highly efficient detectors up to 40 GHz. The current-voltage characteristic for a backward diode is shown in Fig. 1.16 and for comparison the curve for a normal junction diode is also included.

Fig. 1.16. Characteristic curves for a backward diode and normal junction diode. Inset shows graphical symbols used in circuit diagrams

#### Gunn-effect Diode

In certain semiconductors, notably GaAs, electrons can exist in a high-mass low-velocity state as well as their normal low-mass high-velocity state and they can be forced into the high-mass state by a steady electric field of sufficient strength. In this state they form clusters or domains which cross the field at a constant rate causing current to flow as a series of pulses. This is the Gunn effect and one form of diode which makes use of it consists of an epitaxial layer of n-type GaAs grown on a GaAs substrate. A potential of a few volts applied between ohmic contacts to the n-layer and substrate produces the electric field which causes clusters. The frequency of the current pulses so generated depends on the transit time through the n-layer and hence on its thickness. If the diode is mounted in a suitably tuned cavity resonator, the current pulses cause oscillation by shock excitation and r.f. power up to 1 W at frequencies between 10 and 30 GHz is obtainable.

#### Pin Diode

As its name suggests, this is a junction diode with a region of intrinsic semiconductor between the n- and p-regions. When such a diode is reverse-biased the intrinsic layer is depleted of carriers and the diode behaves as a capacitor. When it is forward-biased carriers are injected into the intrinsic region to give a forward resistance which varies linearly between, say, 1 ohm and 10 kilohms with the current through the device. This property makes the diode useful as a modulator or switch in microwave systems and at frequencies between 1 MHz and 20 GHz.

#### Light-emitting Diodes (LEDs)

When a pn junction is forward-biased electrons are driven into the p-region and holes into the n-region as shown in Fig. 1.10. Some of these charge carriers combine in the junction area and in some of the combinations energy is given out in the form of light. By using an alloy of gallium, arsenic and phosphorus as the semiconducting material the emitted light can be made any colour between red and green but maximum electrical-optical efficiency is obtained when the light is red. Lamps and digital displays using this principle are known as *light-emitting diodes*. Such lamps typically consume 25 mA at 4 V and have a very long life.

Blue-emitting LEDs use more exotic semiconductors such as silicon carbide, and are more expensive and less efficient than red and green emitters. They have forward voltages in the region of 5 V.

#### Laser Diodes

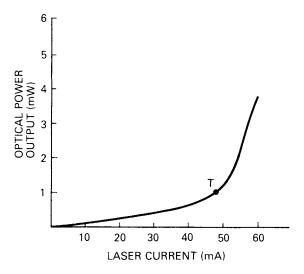

When high-energy photons pass through a material some are absorbed by atoms, which acquire a higher energy level as a result. Normally the excited atoms quickly return to their normal state by re-emitting a photon. In some semiconductors the high energy level can be sustained so that a photon released from one atom can stimulate the release of another from an adjacent atom, and so on. The process is triggered by normal LED action and builds up to a point governed by the current available from the diode supply. In an injection-laser LED a pn junction is formed in a GaAs crystal, the end faces of which (parallel to the junction plane) are polished so that they act as semi-transparent mirrors and feed back into the junction region some of the emitted light. The photons bounce back and forth in what amounts to an optical cavity resonator, and above a certain threshold bias current they are released in a continuous stream of coherent light from the end of the crystal; a typical operating curve is shown in Fig. 1.17. The most popular application for laser diodes is in audio compact disk (CD) players, where they provide a very narrow infra-red light beam to read the information from micro-pits on the disk surface.

Fig. 1.17. Laser diode operating curve: note the abrupt threshold region at point T

## **Basic Principles of Transistors**

#### **BIPOLAR TRANSISTORS**

#### Introduction

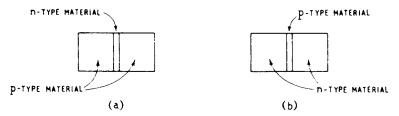

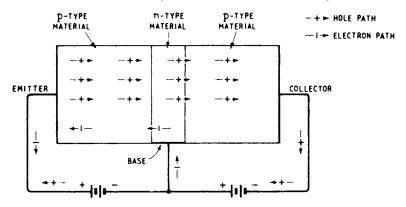

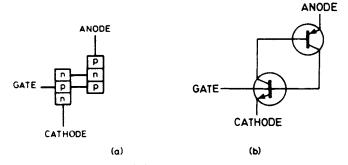

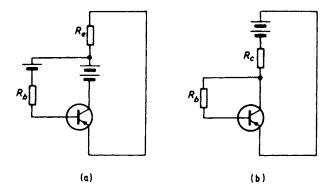

Chapter 1 showed that a junction between n-type and p-type materials has asymmetrical conducting properties enabling it to be used for rectification. A bipolar transistor includes two such junctions arranged as shown in Fig. 2.1. Fig. 2.1(a) illustrates one basic type consisting of a layer of n-type material sandwiched between two

Fig. 2.1. Theoretical diagrams illustrating the structure of (a) a pnp and (b) an npn transistor

layers of p-type material: such a transistor is referred to as a *pnp-type*.

A second type, illustrated in Fig. 2.1(b), has a layer of p-type material sandwiched between two layers of n-type semiconducting material: such a transistor is referred to as an npn-type.

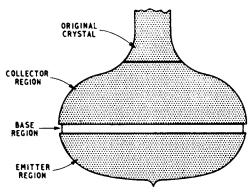

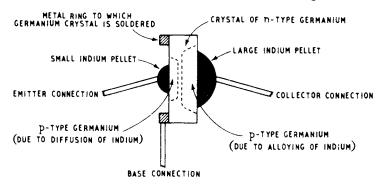

In both types, for successful operation, the central layer must be thin. However, it is not possible to construct bipolar transistors by placing suitably treated layers of semiconducting material in contact. One method which is employed is to start with a single crystal of, say, n-type germanium and to treat it so as to produce regions of p-type conductivity on either side of the remaining region of n-type conductivity.

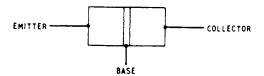

Electrical connections are made to each of the three different regions as suggested in Fig. 2.2. The thin central layer is known as

Fig. 2.2. Electrical connections to a bipolar transistor

the *base* of the transistor, one of the remaining two layers is known as the *emitter* and the remaining (third) layer is known as the *collector*. The transistor may be symmetrical and either of the outer layers may then be used as emitter: the operating conditions determine which of the outer layers behaves as emitter, because in normal operation the emitter-base junction is forward-biased whilst the base-collector junction is reverse-biased. In practice most bipolar transistors are unsymmetrical with the collector junction larger than the emitter junction and it is essential to adhere to the emitter and collector connections prescribed by the manufacturer.

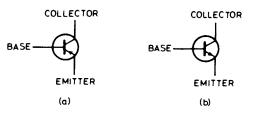

Fig. 2.3. Circuit diagram symbols for (a) pnp and (b) an npn bipolar transistor

The symbols used for bipolar transistors in circuit diagrams are given in Fig. 2.3. The symbol shown at (a), in which the emitter arrow is directed towards the base, is used for a pnp transistor and the symbol shown at (b), in which the emitter arrow is directed away from the base, is used for an npn transistor.

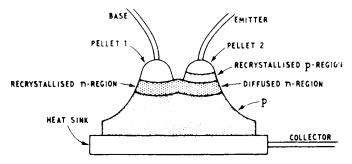

An account of the principal methods used in the manufacture of transistors is given in Appendix A.

#### **Operation** of a pnp Transistor

Fig. 2.4 illustrates the polarity of the potentials which are necessary in a pnp-transistor amplifying circuit. The emitter is biased slightly positively with respect to the base: this is an example of forward bias and the external battery opposes the internal potential barrier associated with the emitter-base junction. A considerable current therefore flows across this junction and this is carried by holes from

Fig. 2.4. Hole and electron paths in a pnp transistor connected for amplification

the p-type emitter (which move to the right into the base) and by electrons from the n-type base (which move to the left into the emitter). However, because the impurity concentration in the emitter is normally considerably greater than that of the base (this is adjusted during manufacture), the holes carrying the emitter-base current greatly outnumber the electrons and we can say with little error that the current flowing across the emitter-base junction is carried by holes moving from emitter to base. Because holes and electrons play a part in the action, this type of transistor is known as *bipolar*.

The collector is biased negatively with respect to the base: this is an example of reverse bias and the external battery aids the internal potential barrier associated with the base-collector junction. If the emitter-base junction were also reverse-biased, no holes would be injected into the base region from the emitter and only a very small current would flow across the base-collector junction. This is the reverse current (described in Chapter 1): it is a saturation current independent of the collector-base voltage. However, when the emitter-base junction is forward-biased, the injected holes have a marked effect on the collector current. Because the base is a particularly thin layer most of the injected holes cross the base by diffusion and on reaching the collector-base junction are swept into the collector region. The reverse bias of the base-collector junction ensures the collection of all the holes crossing this junction, whether these are present in the base region as a result of breakdown of covalent bonds by virtue of thermal agitation or are injected into it by the action of the emitter. A few of the holes which leave the emitter combine with electrons in the base and so cease to exist but the majority of the holes (commonly more than 95 per cent) succeed in reaching the collector. Thus the increase in collector current due to hole-injection by the emitter is nearly equal to the current flowing across the emitter-base junction. The balance of the emitter carriers (equal to, say, 5 per cent) is neutralised by electrons in the base region and to maintain charge neutrality more electrons flow into the base, constituting a base current.

Thus a small current flowing in the base controls a much larger collector current: this is the essence of transistor action and from what has been said above it is clear that to achieve high current gain we need a heavily doped emitter area and a very thin but lightly doped base region. In early alloy-junction transistors the base thickness exceeded  $10^{-4}$  cm but in more modern planar types it is less than  $10^{-5}$  cm.

The collector current, even though it may be considerably increased by forward bias of the emitter-base junction, is still independent of the collector voltage. This is another way of saying that the output resistance of the transistor is extremely high: it can in fact be several megohms. The input resistance is approximately that of a forwardbiased junction diode and is commonly of the order of  $25 \Omega$ . A small change in the input (emitter) current of the transistor is faithfully reproduced in the output (collector) current but, of course, at a slightly smaller amplitude. Clearly such an amplifier has no current gain but because the output resistance is many times the input resistance it can give voltage gain. To illustrate this suppose a 1-mV signal source is connected to the 25- $\Omega$  input. This gives rise to an emitter current of 1/25 mA, i.e. 40 µA. The collector current is slightly less than this but as an approximation suppose the output current is also 40  $\mu$ A. A common value of load resistance is 5 k $\Omega$  and for this value the output voltage is given by  $5,000 \times 40 \times 10^{-6}$ , i.e. 200 mV, equivalent to a voltage gain of 200.

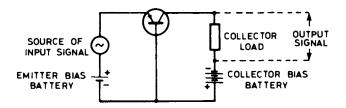

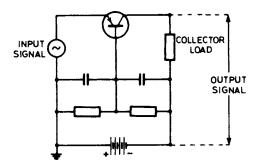

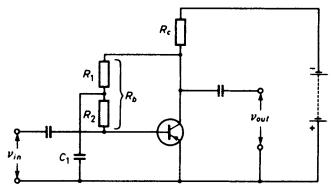

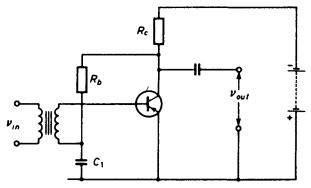

#### Bias Supplies for a pnp Transistor

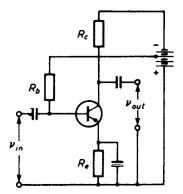

Fig. 2.5 shows a pnp transistor connected to supplies as required in one form of amplifying circuit. For forward bias of the emitter-

27

base junction, the emitter is made positive with respect to the base; for reverse bias of the base-collector junction, the collector is made negative with respect to the base. Fig. 2.5 shows separate batteries used to provide these two bias supplies and it is significant that the batteries are connected in series, the positive terminal of one being connected to the negative terminal of the other. The base voltage in fact lies between that of the collector and the emitter and thus a single battery can be used to provide the two bias supplies by connecting it between emitter and collector, the base being returned to

Fig. 2.5. Basic circuit for using a pnp transistor as an amplifier

a tapping point on the battery or to a potential divider connected across the battery. The potential divider technique (Fig. 2.6) is often used in transistor circuits and a pnp transistor operating with the emitter circuit earthed requires a negative collector voltage. The

Fig. 2.6. The circuit of Fig. 2.5 using a single battery and a potential divider providing base bias

arrow in the transistor symbol shows the direction of conventional current flow, i.e. is in the opposite direction to that of electron flow through the transistor.

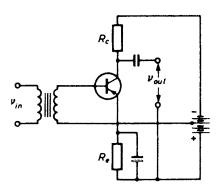

#### **Operation** of an npn Transistor

The action of an npn junction transistor is similar to that of a pnp type just described but the bias polarities and directions of current flow are reversed. Thus the charge carriers are predominantly electrons and the collector bias voltage for an earthed-emitter circuit must be positive.

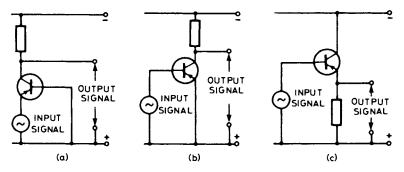

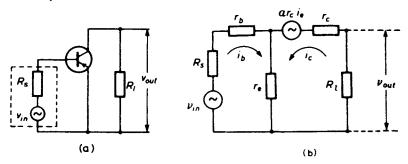

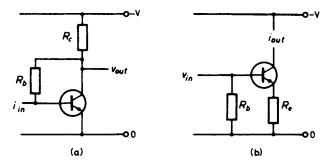

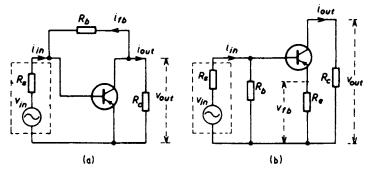

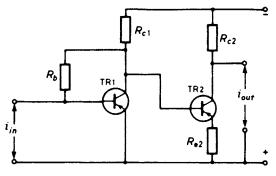

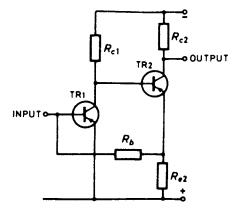

#### Common-base, Common-emitter and Common-collector Amplifiers

So far we have described amplifying circuits in which the emitter current determines the collector current: it is, however, more usual in transistor circuits to employ the external base current to control the collector or emitter current. Used in this way the transistor is a current amplifier because the collector (and emitter) current can easily be 100 times the controlling (base) current and variations in the input current are faithfully portrayed by much larger variations in the output current.

Thus we can distinguish three ways in which the transistor may be used as an amplifier:

- (a) with emitter current controlling collector current,

- (b) with base current controlling collector current,

- (c) with base current controlling emitter current.

It is significant that in all these modes of use, operation of the transistor is given in terms of input and output current. This is an

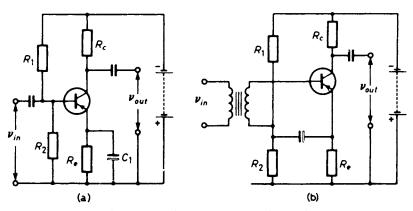

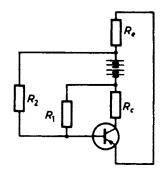

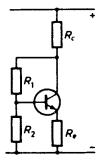

Fig. 2.7. The three basic forms of transistor amplifier; (a) common-base, (b) common-emitter and (c) common-collector (emitter follower). For simplicity base d.c. bias is omitted

inevitable consequence of the physics of the bipolar transistor: such transistors are *current-controlled* devices: by contrast field-effect transistors are voltage-controlled devices.

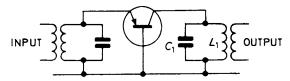

Corresponding to the three modes of operation listed above there are three fundamental transistor amplifying circuits: these are shown in Fig. 2.7. At signal frequencies the impedance of the collector voltage supply is assumed negligibly small and thus we can say for circuit (a) that the input is applied between emitter and base and that the output is effectively generated between collector and base. Thus the base connection is common to the input and output circuits: this amplifier is therefore known as the *common-base* type.

Fig. 2.5 illustrates one significant feature of the common-base circuit, namely that the base acts as a screen between the input and output circuits. The elimination of capacitive coupling between them makes stable v.h.f. and u.h.f. amplification possible.

In (b) the input is again applied between base and emitter but the output is effectively generated between collector and emitter. This is therefore the *common-emitter* amplifier, probably the most used of all transistor amplifying circuits.

In (c) the input is effectively between base and collector, the output being generated between emitter and collector. This is the *common-collector* circuit but it is better known as the *emitter follower*.

#### **Current Amplification Factor**

In a common-base amplifier the ratio of a small change in collector current  $i_c$  to the small change in emitter current  $i_c$  which gives rise to it is known as the current amplification factor  $\alpha$ . It is measured with short-circuited output. Thus we have

$$\alpha = \frac{i_c}{i_e} \tag{2.1}$$

As we have seen  $i_c$  is very nearly equal to  $i_e$ . Thus  $\alpha$  is nearly equal to unity and is seldom less than 0.95. In approximate calculations  $\alpha$  is often taken as unity.

In a common-emitter amplifier the ratio of a small change in collector current  $i_c$  to the small change in base current  $i_b$  which gives rise to it is represented by  $\beta$ . It is also measured with short-circuited output and indicates the maximum possible current gain of the transistor. Thus

$$\beta = \frac{i_c}{i_b} \tag{2.2}$$

We have seen how the emitter current of a transistor effectively divides into two components in the base region. Most of it passes into the collector region and emerges as external collector current. The remaining small fraction forms an external base current. This division applies equally to steady and signal-frequency currents. Thus we have

$$i_e = i_c + i_b \tag{2.3}$$

From Eqns 2.1, 2.2 and 2.3 we can deduce a relationship between  $\alpha$  and  $\beta$  thus

$\beta = \frac{i_c}{i_b} = \frac{i_c}{i_e - i_c}$ But  $i_c = \alpha i_e$  $\therefore \beta = \frac{\alpha i_e}{i_e - \alpha i_e}$  $= \frac{\alpha}{1 - \alpha}$ (2.4)

As  $\alpha$  is nearly equal to unity there is little error in taking  $\beta$  as given by

$$\beta = \frac{1}{1 - \alpha} \tag{2.5}$$

Thus for a transistor for which  $\alpha = 0.98$

$$\beta = \frac{1}{1 - 0.98} = \frac{1}{0.02} = 50$$

In practice values of  $\beta$  lie between 20 and 500.  $\beta$  is one of the properties of a transistor normally quoted in manufacturer's literature: here it is usually known as  $h_{f.}$ .

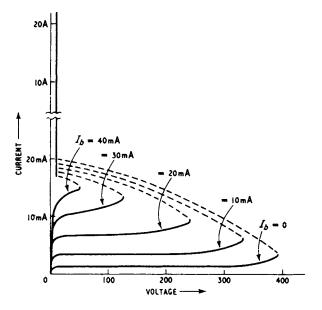

#### Collector Current-Collector Voltage Characteristics

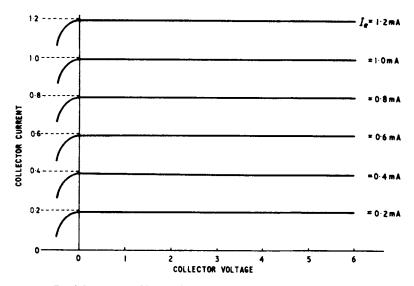

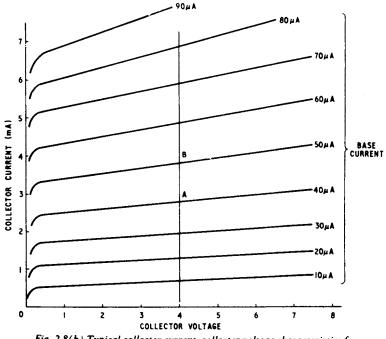

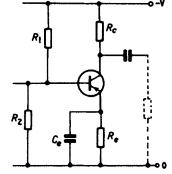

Fig. 2.8(a) illustrates the way in which the collector current of a bipolar transistor varies with collector voltage for given values of the emitter current. The characteristics are straight, horizontal and equidistant. The fact that the the curves are horizontal shows that collector current is independent of collector voltage: in other words, the collector a.c. resistance is very high. The regular spacing implies low distortion if the device is used as an analogue amplifier. Fig. 2.8(b) illustrates the way in which the collector current of a bipolar transistor varies with collector voltage for given values of base current. These characteristics are of the same general shape as those of Fig. 2.8(a).

31

Fig. 2.8(a) A set of  $l_c - V_c$  characteristics for a common-base amplifier

Fig. 2.8(b) Typical collector current-collector voltage characteristics for common-emitter connection

#### 32 Principles of Transistor Circuits

A number of parameters of the transistor can be obtained from these characteristics. For example the slope of the curves is not so low as for the common-base connection showing that the collector a.c. resistance is smaller: it is in fact approximately 30 k $\Omega$ . To deduce  $\beta$  consider the intercepts made by the characteristics on the vertical line drawn through  $V_c = 4$  V. When the base current is 40  $\mu$ A (point A) the collector current is 2.5 mA and when  $I_b$  is 50  $\mu$ A (point B)  $I_c$  is 3.5 mA. A change of base current of 10  $\mu$ A thus causes a change in collector current of 1 mA: this corresponds to a value of  $\beta$  of 100.

#### Collector Current-Base Voltage Characteristics

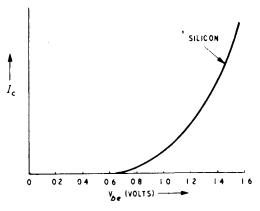

Fig. 2.9 gives the  $I_c - V_{be}$  characteristics for a silicon transistor. This shows that the relationship between base voltage and collector current is not linear. It also shows that collector current does not start until the base voltage exceeds about 0.7 V. This was pointed out in Chapter 1 in respect of silicon junction diodes.

Fig. 2.9.  $I_c - V_{be}$  curves for a silicon transistor

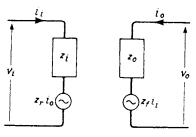

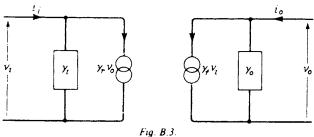

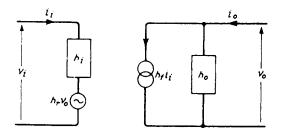

#### Equivalent Circuit of a Transistor

For calculating the performance of transistor circuits, it is useful to regard the transistor as a three-terminal network which is specified in terms of its input resistance, output resistance and current gain all fundamental properties which can readily be measured. The properties of such a network are expressed in a number of ways notably as z parameters, y parameters or h parameters. The basic equations for these parameters are given in Appendix B and this shows that these parameters, in spite of their variety, express the same four properties of the network, namely its input resistance, output resistance, forward gain and reverse gain.

One of the disadvantages of this method of expressing transistor properties is that the values of the fundamental properties which apply to the common-base connection do not apply to the commonemitter connection or to the common-collector connection and three sets of values are therefore required in a complete expression of a transistor's properties. Moreover the numerical values of these properties vary with emitter current and frequency and can be regarded as constant only over a narrow frequency and emitter-current range.

An alternative approach to the problem of calculating transistor performance is to deduce an equivalent network which has a behaviour similar to that of the transistor. The constants of such a network can often be directly related to the physical construction of the transistor but they cannot be directly measured: they can,

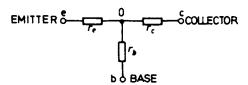

Fig. 2.10. A three-terminal passive network which can be used to build an equivalent circuit for a transistor

however, be deduced from measurements on the transistor. If the network is truly equivalent it will hold at all frequencies and by applying Kirchhoff's laws or other network theorems to this equivalent circuit we can calculate the performance of the circuit. Much useful work is possible by representing a transistor as a simple T-network of resistance as shown in Fig. 2.10.

The transistor cannot, however, be perfectly represented by three resistances only because such a network cannot generate power (as a transistor can) but can only dissipate power. In other words the network illustrated in Fig. 2.10 is a *passive* network and to be accurate the equivalent network must include a source of power, i.e. must be *active*.

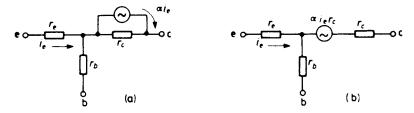

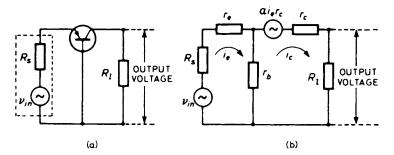

The source of power could be shown as a constant-current source connected in parallel with the collector resistance  $r_c$  as in Fig. 2.11(a) and the current so supplied is, as we have already seen, equal to  $\alpha i_e$ , where  $\alpha$  is the current amplification factor of the transistor

Fig. 2.11. A three-terminal active network which can be used as an equivalent circuit for a transistor (a) including a constant-current generator, and (b) a constantvoltage generator

and  $i_e$  is the current in the emitter circuit, i.e. in the emitter resistance  $r_e$ . Alternatively the source of power can be represented as a constant-voltage generator connected in series with  $r_c$  as shown in Fig. 2.11(b).

Such a voltage has precisely the same effect as the constantcurrent generator, provided the voltage is given the correct value, and the value required is equal to  $\alpha i_e r_c$  as can be shown by applying Thevenin's theorem to Fig. 2.11(a).

In some books on transistors the voltage generator is given as  $r_m i_e$ , where  $r_m$  is known as the *mutual* or *transfer resistance*<sup>\*</sup> and is equal to  $\alpha r_c$ . The mutual resistance may be defined as the ratio of the e.m.f. in the collector circuit to the signal current in the emitter circuit which gives rise to it. This may be regarded as the dual of the mutual conductance  $g_m$  of a field-effect transistor which is defined as the ratio of the current in the drain circuit to the signal voltage in the gate circuit which causes it.

This network is quite satisfactory for calculating the performance of transistor amplifiers at low frequencies such as audio amplifiers because the reactances of the internal capacitances have, in general, negligible effects on performance.

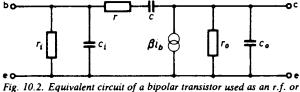

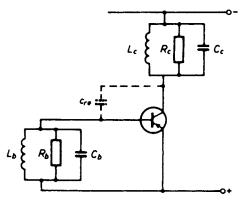

At higher frequencies, however, and in particular at radio frequencies, it is necessary to include such capacitances in the T-network to obtain accurate answers.

Of the various internal capacitances within a bipolar transistor, that between the collector and the base has the greatest effect on the high-frequency performance.

In a transistor r.f. amplifier the capacitance between collector and base provides feedback from the output to the input circuit. This is

\* The word 'transistor' is, in fact, derived from 'transfer resistance'.

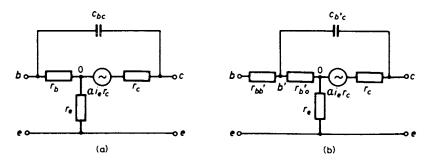

Fig. 2.12. T-section equivalent circuit of a transistor showing collector capacitance, (a) returned to base input terminal and (b) returned to a tapping point on the base resistance

illustrated in Fig. 2.12(a) in which the capacitance  $c_{bc}$  is shown connected directly between collector and base terminals. However, a better approximation to the performance of a transistor at high frequencies is obtained by assuming that the collector capacitance is returned to a tapping point b' on the base resistance as shown in Fig. 2.12(b).

This modifies the feedback which now occurs via  $c_{b'c}$  and  $r_{bb'}$ in series and the high-frequency performance of the transistor is now dependent on the time constant  $r_{bb'} c_{b'c}$  which is probably the most important characteristic of a transistor intended for highfrequency use.

Values of  $r_e$ ,  $r_b$  and  $r_c$

The networks of Fig. 2.11 can be used in analyses of transistor circuits. The resistances represent differential, i.e. a.c. quantities and, for a given value of mean emitter current  $I_e$ , are constant provided that the variations in voltage or current which occur during operation of the transistor are small.

The value of  $r_e$  for all bipolar transistors, irrespective of size and type, is given by

$$r_e = \frac{kT}{eI_e}$$

where k = Boltzmann's constant, i.e.  $1.374 \times 10^{-23} \text{ J/}^{\circ}\text{C}$

e = charge on the electron, i.e.  $1.59 \times 10^{-19}$  C

and T = absolute temperature.

Thus  $r_e$  is directly proportional to the absolute temperature and inversely proportional to the emitter current. The coefficient kT/ehas the dimensions of a voltage and if we substitute numerical values for k and e this voltage is 25 mV at a temperature of 20°C. Thus we have

$$r_e(\Omega) = \frac{25 \,(\mathrm{mV})}{I_e \,(\mathrm{mA})}$$

If  $I_e = 1$  mA,  $r_e$  is 25  $\Omega$  (at 20°C).

The value of  $r_c$  is also inversely proportional to  $I_e$  in simple transistors but the value depends on the impurity grading in the base region and is very high for diffused-base transistors.

The value of  $r_b$  is largely independent of  $I_e$  and is a function of the size and geometry of the transistor. For small silicon transistors it is unlikely to exceed 100  $\Omega$  but for a large power transistor  $r_b$  may be as low as 5  $\Omega$ .

The values of  $r_e$ ,  $r_b$  and  $r_c$  cannot be measured directly because it is impossible to obtain a connection to the point O (in Fig. 2.12) but the values can be deduced from measurements made at the transistor terminals.

Although the bipolar transistor is a current-controlled device there are occasions (e.g. when it is used as a voltage amplifier) when it is useful to be able to express the performance in terms of the signal voltage applied between base and emitter. For such calculations we need to know the mutual conductance  $g_m$  of the transistor: this is the ratio of a small change in collector current to the change in base-emitter voltage which causes it.

The mutual conductance of a transistor is given by

$$g_m = \frac{\alpha_o}{r_e}$$

where  $\alpha_o$  is the current amplification factor at low frequencies.  $\alpha_o$  is very nearly equal to unity and thus we may say

$$g_m \approx \frac{1}{r_e}$$

We know, from the top of this page that  $r_e$  is inversely proportional to the mean emitter current  $I_e$  according to the relationship

$$r_{e}(\Omega) = \frac{25 \,(\mathrm{mV})}{I_{e} \,(\mathrm{mA})}$$

Eliminating  $r_e$  between the last two expressions we have

$$g_m (A/V) \approx \frac{I_e (mA)}{25 (mV)}$$

which is perhaps more conveniently expressed

$$g_m (mA/V) \approx 40 I_e (mA)$$

Thus for an emitter current of 1 mA the mutual conductance is 40 mA/V.

## Frequency f<sub>T</sub>

Modern circuitry makes extensive use of silicon planar transistors as common-emitter amplifiers and the high-frequency performance is usually expressed in terms of the parameter  $f_T$ , the transition frequency. This is defined as the frequency at which the modulus of  $\beta$ (the current gain of the common-emitter amplifier) has fallen to unity. It thus measures the highest frequency at which the transistor can be used as an amplifier: it also gives the gain-bandwidth product for the transistor.

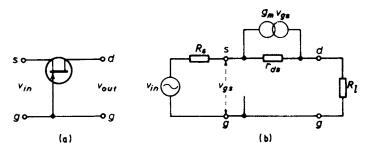

### FIELD-EFFECT TRANSISTORS

# Introduction

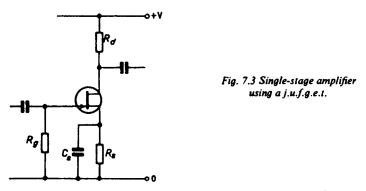

Field-effect transistors operate on principles quite different from those of bipolar transistors. They consist essentially of a channel of semiconducting material, the charge-carrier density of which is controlled by the input signal. The input signal thus determines the conductivity of the channel and hence the current which flows through it from the supply. The connections from the ends of the channel to the supply are known as the source and drain terminals and they correspond to the emitter and collector terminals of a bipolar transistor. The control terminal is known as the gate. The potential on the gate can control the channel conductivity via a reverse-biased pn junction: transistors using this principle are termed junction-gate field-effect transistors (j.u.g.f.e.t.s). Alternatively the gate potential can control the channel conductivity via a capacitance link: transistors using this principle are termed insulated-gate field-effect transistors (i.g.f.e.t.s). F.e.t.s in general can be regarded as voltage-controlled variable resistors.

# 38 Principles of Transistor Circuits

There is only one type of charge carrier in an f.e.t. namely electrons in an n-channel device and holes in a p-channel device. Thus f.e.t.s can be termed unipolar\* transistors: those previously described in this chapter are, of course, bipolar. An important consequence of the single type of charge carrier is that an f.e.t. can introduce less noise than bipolar types. Because there are no minority carriers, f.e.t.s are also free of the carrier-storage effects which limit the switching times of bipolar transistors.

# Junction-gate Field-effect Transistors (j.u.g.f.e.t.s)

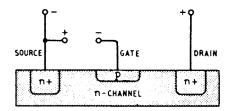

The structure of an n-channel j.u.g.f.e.t. is illustrated in Fig. 2.13. This shows a slice of high-resistance n-type silicon with ohmic contacts formed by highly doped (n +) regions near the two ends: these provide the source and drain connections to the external

Fig. 2.13. Structure of an n-channel j.u.g.f.e.t. with bias polarities indicated

circuit. A region of p-type conductivity is formed between the ohmic contacts: this forms the gate connection and is reverse-biased, i.e. negatively biased with respect to the source connection. When the source and drain terminals are connected to a supply, current flows longitudinally through the slice, being carried by the free electrons of the n-type material. However, near the p-region there is a depletion area, i.e. an area free of charge carriers and if the reverse bias of the gate is increased the depletion area spreads, confining the longitudinal current to a small cross-sectional area of the slice and reducing its amplitude. If the reverse bias is increased sufficiently the depletion area spreads to the whole cross-section of the slice and cuts off the current completely. The gate-source voltage required to do this is known as the pinch-off voltage. By connecting a signal

<sup>\*</sup> Strictly this should be monopolar if we are using Greek prefixes.

source in series with the gate bias the effective width of the channel can be modulated and the signal waveform is impressed on the current. If the current is passed through a suitable external impedance, the voltage generated across it is a magnified version of that of the signal source.

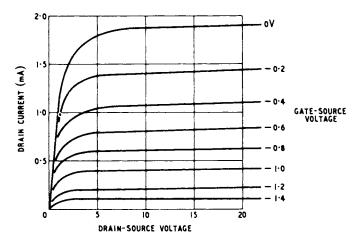

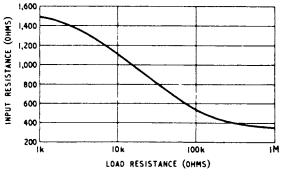

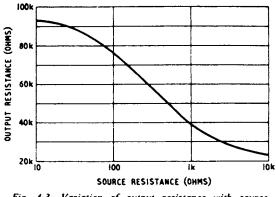

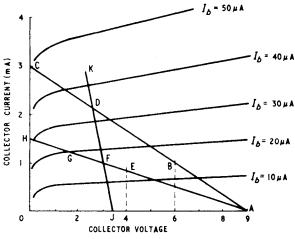

The input resistance of a j.u.g.f.e.t. is that of a reverse-biased pn junction and can be very high: a typical value is  $10^{10} \Omega$  with a shunt capacitance of say 5 pF. The characteristics have the same general shape as those of a bipolar transistor (Fig. 2.14) but, of course, the control parameter here is the gate voltage not current. If the gate terminal of the transistor illustrated in Fig. 2.13 is biased positively with respect to the source, the pn junction is forward biased giving a very low input resistance.

Fig. 2.14. Typical characteristics for a field-effect transistor

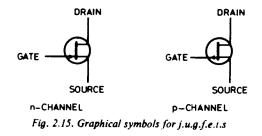

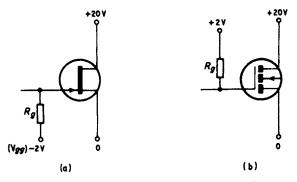

There is a complementary type of j.u.g.f.e.t. with a p-type channel and n-type gate: this requires a positive gate-source voltage to cut off the channel current. The graphical symbols for both types of j.u.g.f.e.t. are given in Fig. 2.15.

The j.u.g.f.e.t. takes a significant drain current with zero gate bias and, for an n-channel device, a negative bias is required to cut the current off. When the f.e.t. is used as an amplifier the gate bias is normally between zero and cut off and lies outside the range of the drain-source voltage; for example typical voltages are  $V_g = -1 V$ ,  $V_s$ = 0 and  $V_d = +20 V$ . Devices with this property are said to operate in the *depletion mode*. The base bias voltage for a bipolar transistor lies between that of the emitter and the collector.

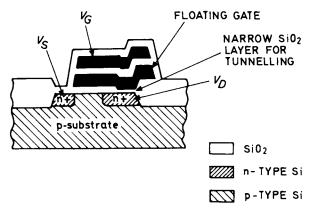

# Insulated-gate Field-effect Transistors (i.g.f.e.t.s)

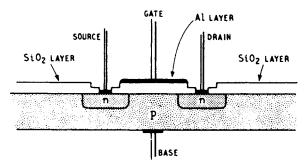

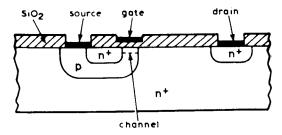

A cross-section of an i.g.f.e.t. is shown in Fig. 2.16. It consists of a base (substrate) layer of p-type silicon into the surface of which two

Fig. 2.16. Structure of enhancement-type n-channel i.g.f.e.t.

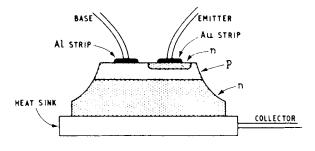

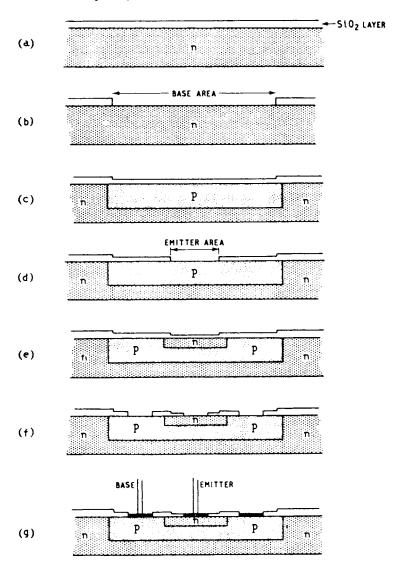

closely spaced stripes of n-type conductivity are diffused. Ohmic connections are made to the n-regions to give source and drain connections, and to the p-type substrate to give a base connection. The device is sealed by a silicon dioxide coating and a thin layer of aluminium between the n-regions provides a gate connection. The device can be manufactured by the techniques used for planar transistors described in Appendix A.

The substrate, the silicon dioxide layer and the aluminium skin form a parallel-plate capacitor. The voltage applied between gate and base controls the conductivity of the surface area of the substrate between the n-regions and hence the current which flows between source and drain when these are connected to a supply. If the gatebase voltage is zero the only drain current is the leakage current of one of the pn junctions and this, in a silicon device, is very small indeed. If the gate is made positive with respect to the base, positive charge carriers are repelled into the body of the substrate and

negative charge carriers are attracted to its surface either from thermal breakdown of the p-material or from the n-regions. In this way a layer of mobile charge carriers is induced on the surface of the substrate and this makes ohmic contact with the diffused nregions. The induced layer provides the conducting channel between the source and drain terminals and permits drain current to flow. The induced layer is known as an *inversion layer* because it changes its conductivity from p-type to n-type as the gate voltage is increased positively from zero. Increase in gate voltage increases the number of charge carriers in the induced layer, increasing channel conductivity and drain current. The gate voltage thus controls the drain current and the characteristics have a form similar to those of a j.u.g.f.e.t. A significant feature of the behaviour of this type of i.g.f.e.t. is that drain current is zero in the absence of a gate voltage and that a forward (positive for an n-channel device) gate bias is necessary to give working values of drain current: this type of operation is known as the enhancement mode.

For an enhancement i.g.f.e.t. to obtain a working value of drain current, the gate voltage must lie between the source and drain potentials. This compares with bipolar transistors and contrasts with depletion devices such as j.u.g.f.e.t.s.

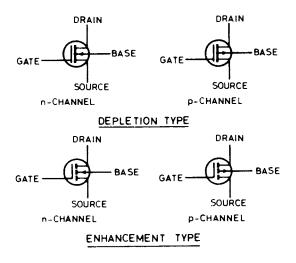

It is, however, possible in the manufacture of an i.g.f.e.t. to produce a thin n-type layer on the surface of the p-type substrate. This provides a conducting channel between source and drain and ensures that a useful drain current flows even at zero gate-base voltage. Negative gate bias reduces channel conductivity and drain current and in the limit will change the conductivity of the channel to p type, reducing drain current to zero: this is the depletion mode of operation again. Positive voltages on the gate increase channel conductivity and drain current as in enhancement-mode operation. I.g.f.e.t.s of this type can thus operate in depletion and enhancement modes.

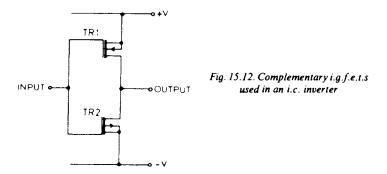

Complementary i.g.f.e.t.s with an n-type substrate and p-type channel are also available, giving a total of four basic types of i.g.f.e.t.: the graphical symbols are shown in Fig. 2.17. The non-conductivity of the enhancement type for zero gate bias is indicated in the symbol by breaks in the rectangle representing the channel.

Input resistances greater than  $10^{12} \Omega$  have been achieved in i.g.f.e.t.s and input capacitances may be as low as 1 pF.

The connection to the substrate provides a second input terminal (the base) to an i.g.f.e.t. and the potential applied to it with respect to the source controls the drain current in the same way as a potential on the gate of a j.u.g.f.e.t. The base terminal is not so sensitive a

Fig. 2.17. Graphical symbols for i.g.f.e.t.s.

control electrode as the gate terminal but is used in certain types of circuit. In many i.g.f.e.t. applications the base terminal is connected to the source terminal internally or externally.

Because of the form of construction of i.g.f.e.t.s they are sometimes known as m.o.s. transistors (metal oxide semiconductor).

The silicon dioxide dielectric of the i.g.f.e.t. is very thin and can easily be broken down by transient voltages on the gate terminal. A practical precaution normally taken in handling such transistors is to keep the leads short-circuited whilst the transistor is being connected into circuit.

## Short-channel f.e.t.s

I.g.f.e.t.s can be manufactured by the planar process and they can be made so small that thousands can be accommodated on a single silicon chip. They are therefore widely used for digital signal storage in computers and similar equipment: typical circuits are described later. In i.g.f.e.t.s used for switching, the length of the conducting channel is important because it controls the switching speed. The length of the channel determines the drain-source resistance when the transistor is conducting and in the type of construction shown in Fig. 2.16 the channel is of considerable length, occupying the whole of the distance between the two n-regions. Much shorter channels are needed in switching transistors and the manufacturers have adopted a number of different geometries to achieve them. In the double-diffused metal-oxide-semiconductor transistor (DMOS) successive diffusions by opposite types of impurity through the same opening in the silicon dioxide layer are used to produce a very short channel the length of which can be closely controlled during manufacture (Fig. 2.18). The channel occupies only a small fraction of the distance

Fig. 2.18. Simplified construction of DMOS transistor

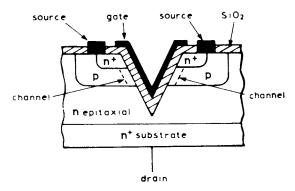

between the n-regions, the remainder being a drift space. In the T-metal-oxide-semiconductor transistor (TMOST) the current flow is normal to the plane of the layers as in bipolar transistors, the source being on top and the drain underneath. The source consists of a number of sites, each associated with a short channel, the parallel connection of which yields the desired low resistance and switching times. A somewhat similar approach is used in the vertical-groove metal-oxide-semiconductor transistor (VMOST) designed to deliver substantial output power, e.g. in audio amplifiers. In this type of transistor a groove-shaped gate projects into the n+, p and epitaxial layers giving very short channel lengths as shown in Fig. 2.19.

Fig. 2.19. Simplified construction of VMOS transistor

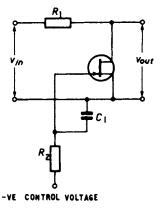

# F.e.t. as a Linear Resistor

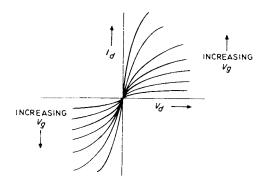

The internal drain-source path of an f.e.t. differs in nature from the corresponding path of a bipolar transistor. It has no rectifying properties and conducts irrespective of the polarity of the applied drain-source voltage. Thus the  $I_d - V_{ds}$  characteristics occupy two quadrants of the current-voltage graph as shown in Fig. 2.20. The

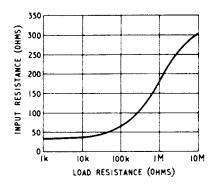

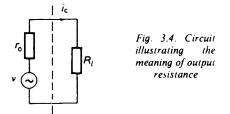

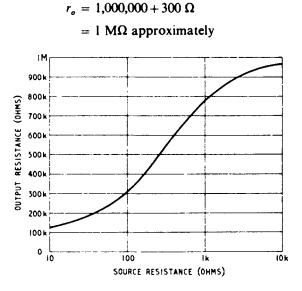

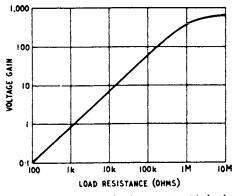

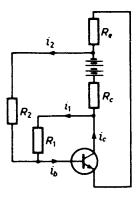

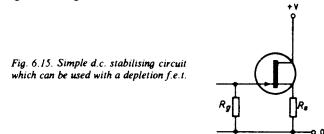

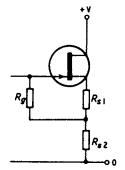

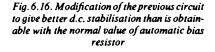

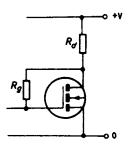

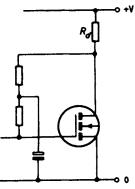

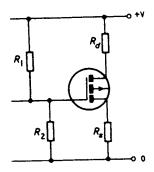

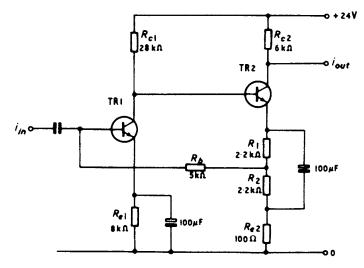

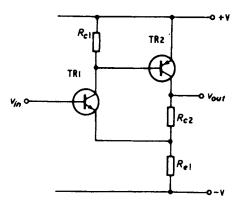

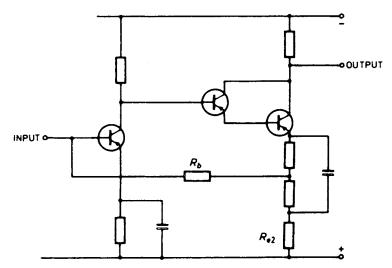

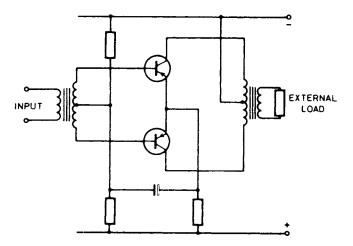

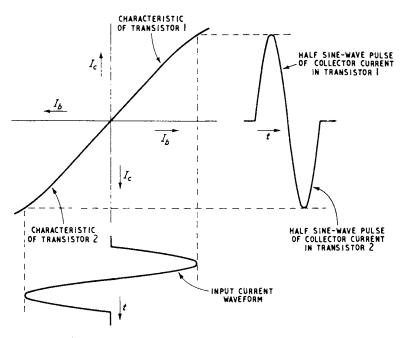

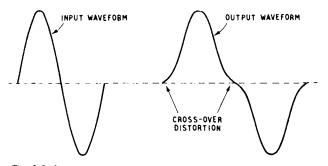

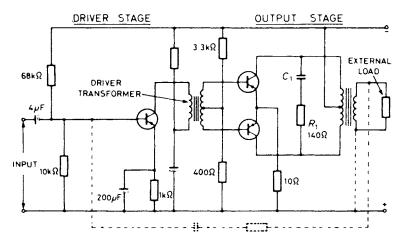

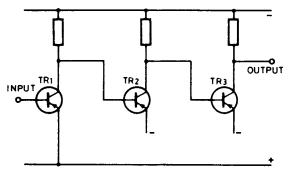

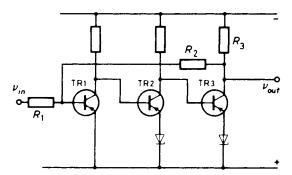

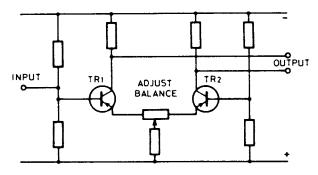

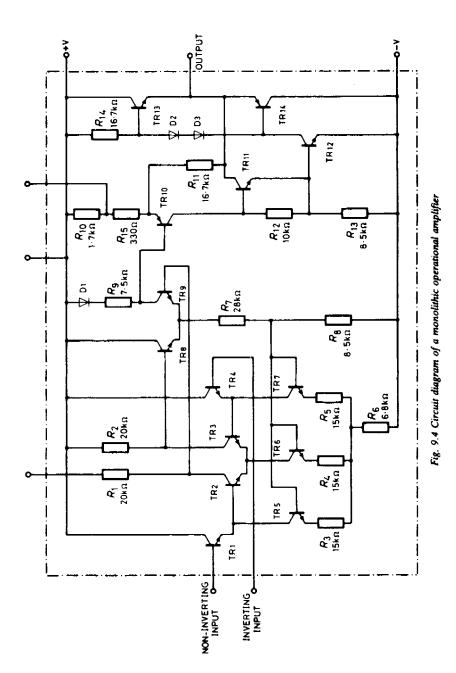

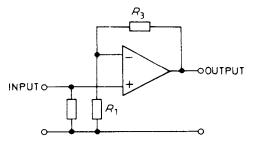

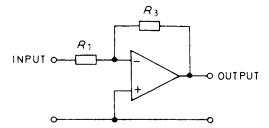

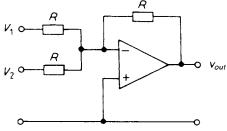

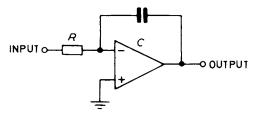

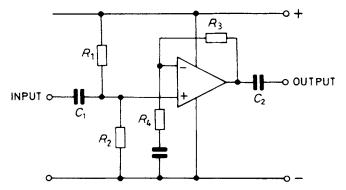

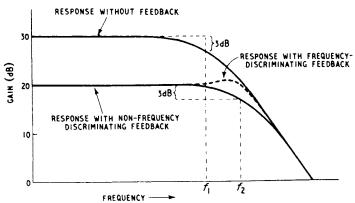

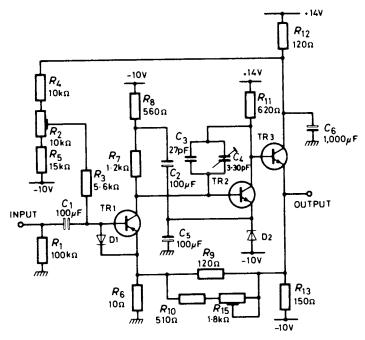

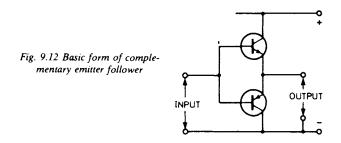

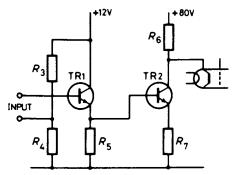

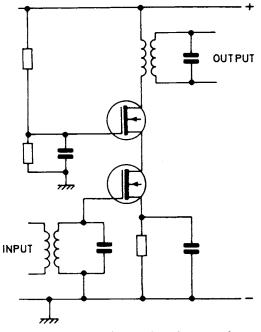

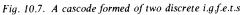

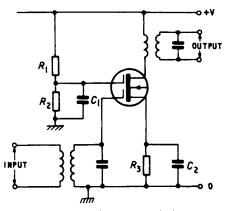

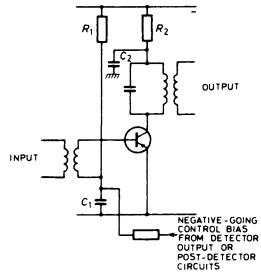

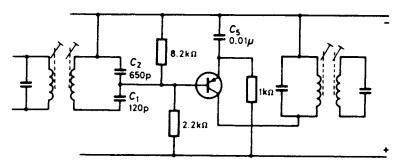

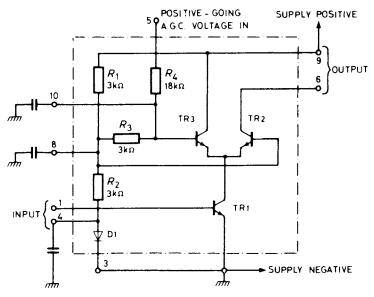

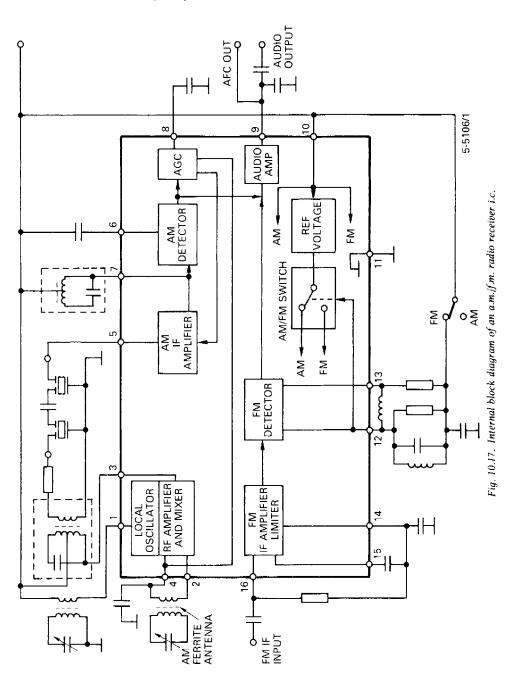

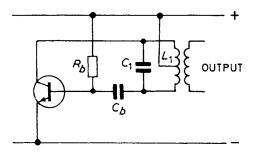

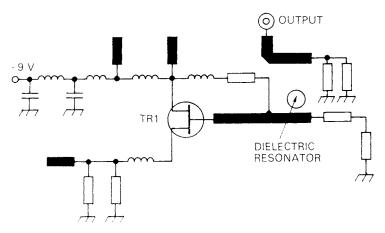

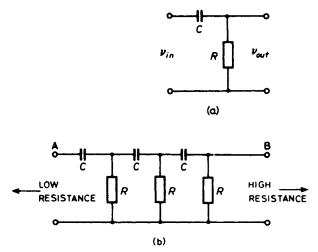

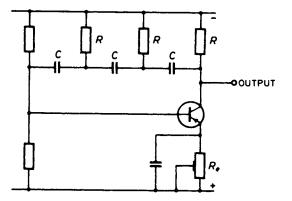

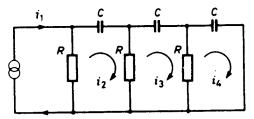

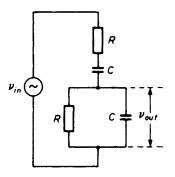

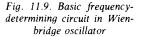

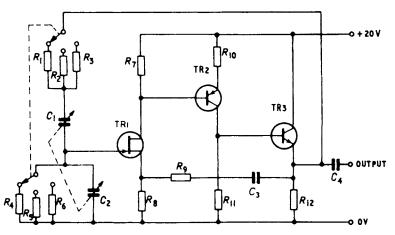

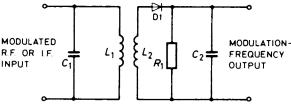

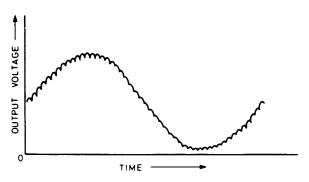

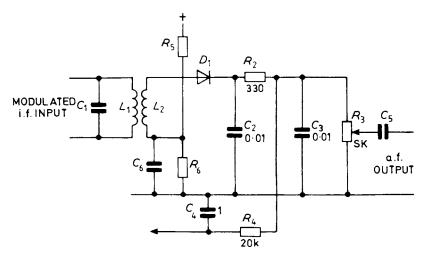

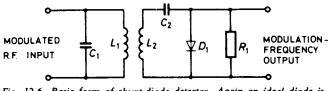

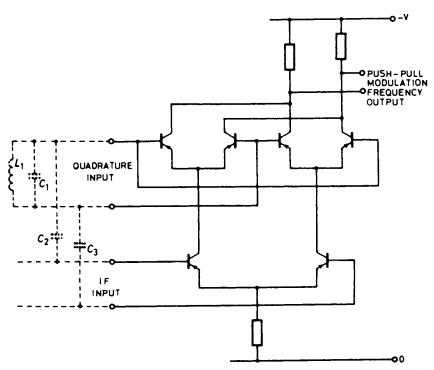

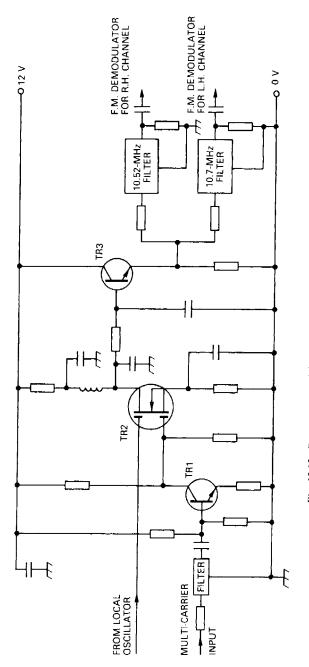

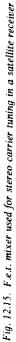

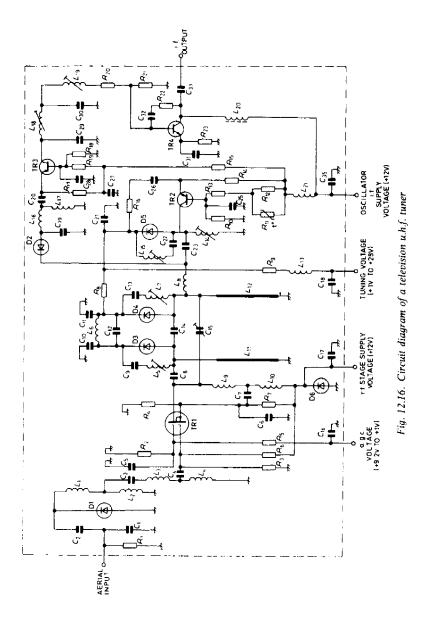

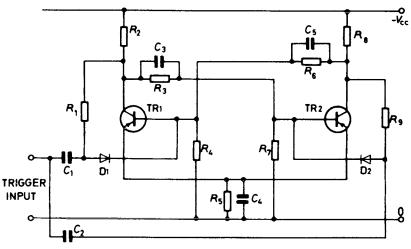

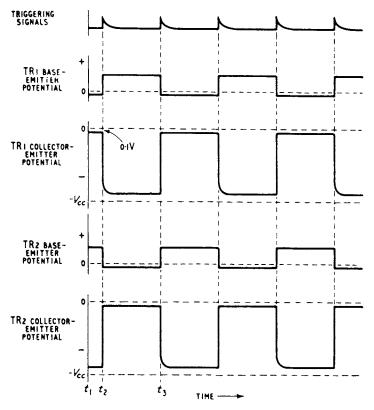

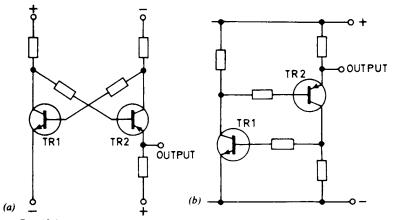

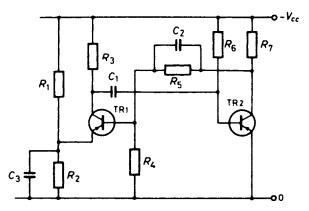

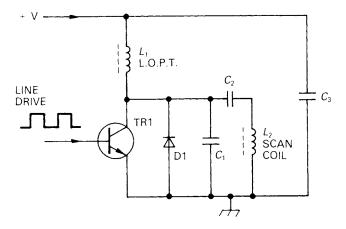

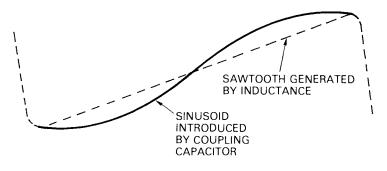

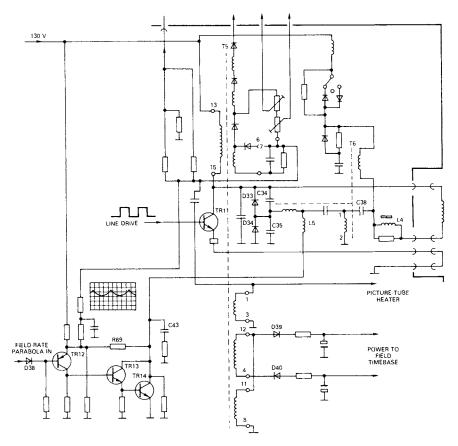

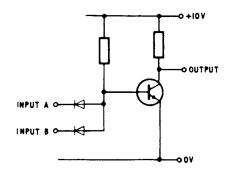

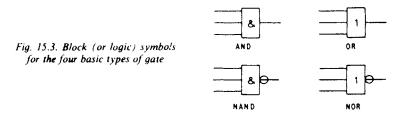

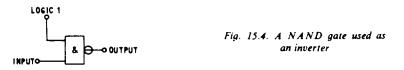

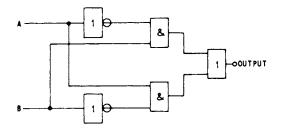

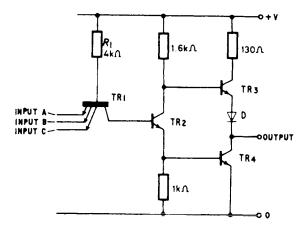

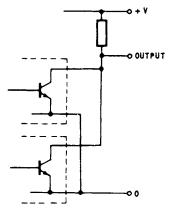

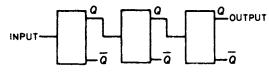

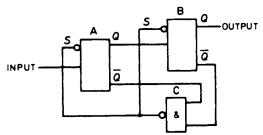

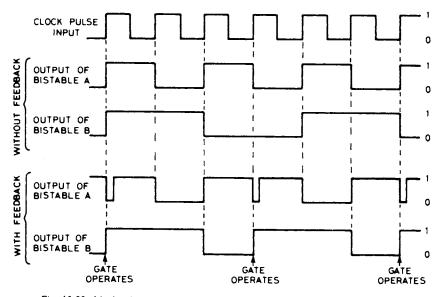

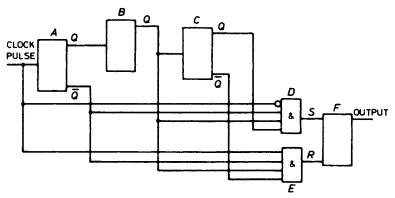

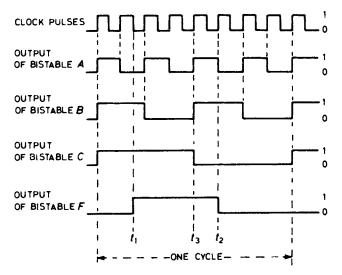

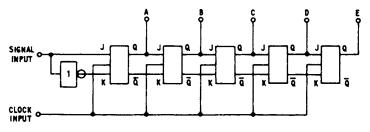

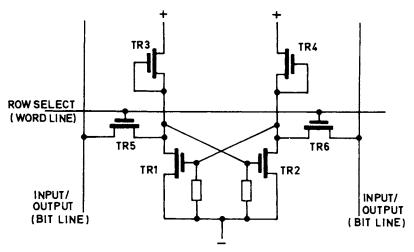

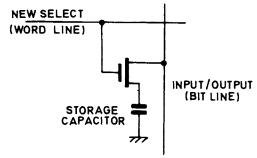

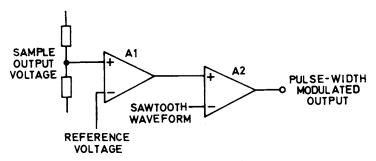

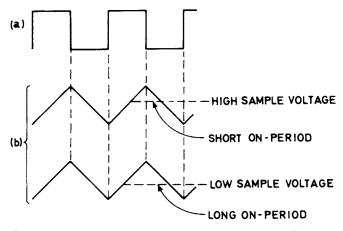

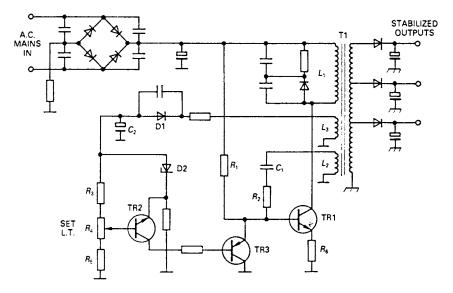

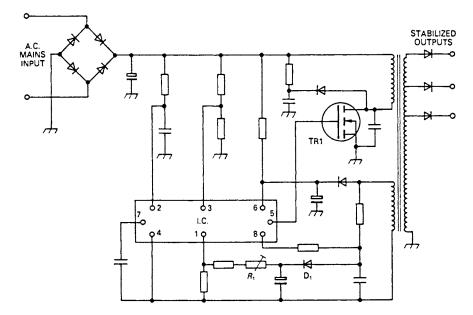

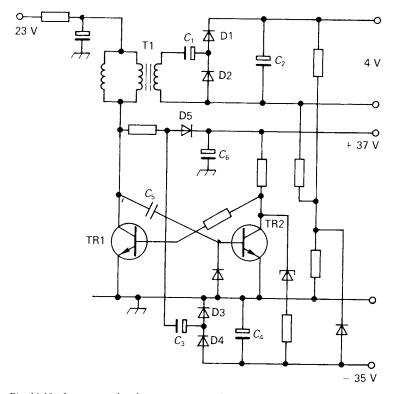

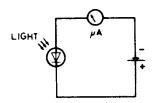

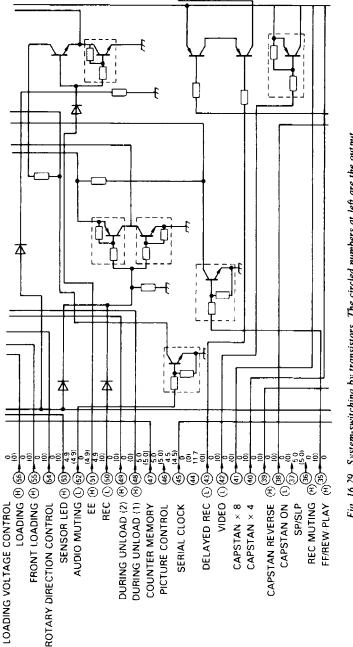

Fig. 2.20.  $I_dV_d$  characteristics of an f.e.t. near the origin