## Vinu V Das Nessy Thankachan Narayan C. Debnath (Eds.)

Communications in Computer and Information Science

148

# Advances in Power Electronics and Instrumentation Engineering

Second International Conference, PEIE 2011 Nagpur, Maharashtra, India, April 2011 Proceedings

Communications in Computer and Information Science 148 Vinu V Das Nessy Thankachan Narayan C. Debnath (Eds.)

## Advances in Power Electronics and Instrumentation Engineering

Second International Conference, PEIE 2011 Nagpur, Maharashtra, India, April 21-22, 2011 Proceedings

Volume Editors

Vinu V Das ACEEE, Trivandrum, Kerala, India E-mail: vinuvdas@theaceee.org

Nessy Thankachan College of Engineering, Trivandrum, Kerala, India E-mail: nessythankachan@gmail.com

Narayan C. Debnath Winona State University, Winona, MN, USA E-mail: ndebnath@winona.edu

e-ISSN 1865-0937 ISSN 1865-0929 ISBN 978-3-642-20498-2 DOI 10.1007/978-3-642-20499-9 Springer Heidelberg Dordrecht London New York

e-ISBN 978-3-642-20499-9

Library of Congress Control Number: 2011925375

CR Subject Classification (1998): D.2, I.4, C.2-3, B.6, C.5.3

The use of general descriptive names, registered names, trademarks, etc. in this publication does not imply, even in the absence of a specific statement, that such names are exempt from the relevant protective laws and regulations and therefore free for general use.

Typesetting: Camera-ready by author, data conversion by Scientific Publishing Services, Chennai, India

Printed on acid-free paper

Springer is part of Springer Science+Business Media (www.springer.com)

<sup>©</sup> Springer-Verlag Berlin Heidelberg 2011

This work is subject to copyright. All rights are reserved, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, re-use of illustrations, recitation, broadcasting, reproduction on microfilms or in any other way, and storage in data banks. Duplication of this publication or parts thereof is permitted only under the provisions of the German Copyright Law of September 9, 1965, in its current version, and permission for use must always be obtained from Springer. Violations are liable to prosecution under the German Copyright Law.

#### Preface

The Second International Conference on Advances in Power Electronics and Instrumentation Engineering (PEIE 2011) was sponsored and organized by The Association of Computer Electronics and Electrical Engineers (ACEEE) and held at Nagpur, Maharashtra, India during April 21-22, 2011.

The mission of the PEIE International Conference is to bring together innovative academics and industrial experts in the field of power electronics, communication engineering, instrumentation engineering, digital electronics, electrical power engineering, electrical machines to a common forum, where a constructive dialog on theoretical concepts, practical ideas and results of the state of the art can be developed. In addition, the participants of the symposium have a chance to hear from renowned keynote speakers. We would like to thank the Program Chairs, organization staff, and the members of the Program Committees for their hard work this year. We would like to thank all our colleagues who served on different committees and acted as reviewers to identify a set of high-quality research papers for PEIE 2011.

We are grateful for the generous support of our numerous sponsors. Their sponsorship was critical to the success of this conference. The success of the conference depended on the help of many other people, and our thanks go to all of them: the PEIE Endowment which helped us in the critical stages of the conference, and all the Chairs and members of the PEIE 2011 committees for their hard work and precious time. We also thank Alfred Hofmann, Janahanlal Stephen, Narayan C. Debnath, and Nessy Thankachan for the constant support and guidance. We would like to express our gratitude to the Springer LNCS-CCIS editorial team, especially Leonie Kunz, for producing such a wonderful quality proceedings book.

February 2011

Vinu V. Das

## PEIE 2011 - Organization

#### **Technical Chairs**

| Hicham Elzabadani     | American University in Dubai |

|-----------------------|------------------------------|

| Prafulla Kumar Behera | Utkal University, India      |

|                       |                              |

## **Technical Co-chairs**

| Natarajan Meghanathan | Jackson State University, USA     |

|-----------------------|-----------------------------------|

| Gylson Thomas         | MES College of Engineering, India |

### **General Chairs**

| Janahanlal Stephen | Ilahiya College of Engineering, India |

|--------------------|---------------------------------------|

| Beno Benhabib      | University of Toronto, Canada         |

### **Publication Chairs**

| R. Vijaykumar          | MG University, India |

|------------------------|----------------------|

| Brajesh Kumar Kaoushik | IIT Roorke, India    |

## **Organizing Chairs**

| Vinu V. Das | The IDES                         |

|-------------|----------------------------------|

| Nessy T.    | Electrical Machines Group, ACEEE |

#### **Program Committee Chairs**

| Harry E. Ruda          | University of Toronto, Canada |

|------------------------|-------------------------------|

| Durga Prasad Mohapatra | NIT Rourkela, India           |

#### **Program Committee Members**

| Shu-Ching Chen   | Florida International University, USA      |  |

|------------------|--------------------------------------------|--|

| T.S.B. Sudarshan | BITS Pilani, India                         |  |

| Habibollah Haro  | Universiti Teknologi Malaysia              |  |

| Derek Molloy     | Dublin City University, Ireland            |  |

| Jagadeesh Pujari | SDM College of Engineering and Technology, |  |

|                  | India                                      |  |

| Nupur Giri       | VESIT, Mumbai, India                       |  |

## Table of Contents

## Full Paper

| Bandwidth Enhancement of Stacked Microstrip Antennas Using<br>Hexagonal Shape Multi-resonators<br><i>Tapan Mandal and Santanu Das</i>                              | 1  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Study of Probabilistic Neural Network and Feed Forward Back<br>Propogation Neural Network for Identification of Characters in License<br>Plate                     | 7  |

| Efficient Minimization of Servo Lag Error in Adaptive Optics Using<br>Data Stream Mining<br>Akondi Vyas, M.B. Roopashree, and B. Raghavendra Prasad                | 13 |

| Soft Switching of Modified Half Bridge Fly-Back Converter<br>Jini Jacob and V. Sathyanagakumar                                                                     | 19 |

| A Novel Approach for Prevention of SQL Injection Attacks Using<br>Cryptography and Access Control Policies<br>K. Selvamani and A. Kannan                           | 26 |

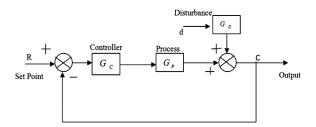

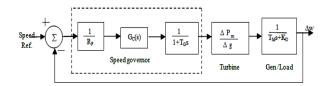

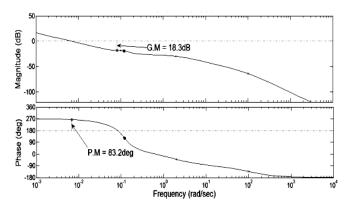

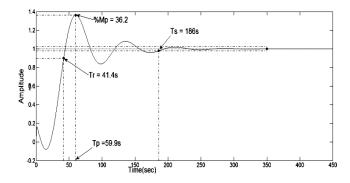

| IMC Design Based Optimal Tuning of a PID-Filter Governor Controller<br>for Hydro Power Plant<br>Anil Naik Kanasottu, Srikanth Pullabhatla, and Venkata Reddy Mettu | 34 |

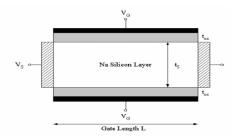

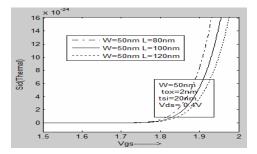

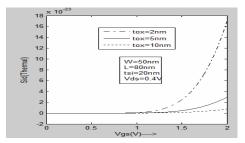

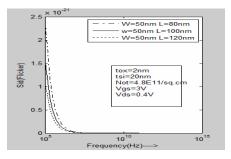

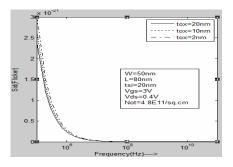

| Thermal and Flicker Noise Modelling of a Double Gate MOSFET<br>S. Panda and M. Ray Kanjilal                                                                        | 43 |

| Optimizing Resource Sharing in Cloud Computing<br>K.S. Arulmozhi, R. Karthikeyan, and B. Chandra Mohan                                                             | 50 |

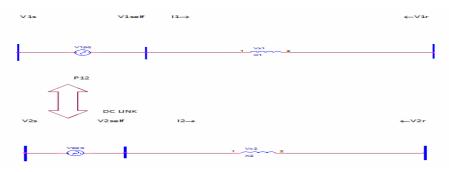

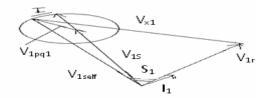

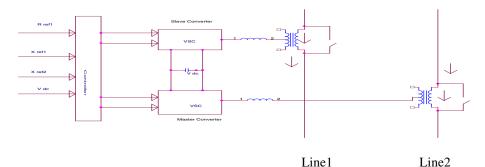

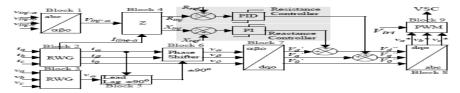

| Design of Controller for an Interline Power Flow Controller and<br>Simulation in MATLAB                                                                            | 56 |

| Short Paper                                                                                                                                                        |    |

| Harmonics Reduction and Amplitude Boosting in Polyphase Inverter<br>Using 60°PWM Technique<br>Prabhat Mishra and Vivek Ramachandran |    |

|-------------------------------------------------------------------------------------------------------------------------------------|----|

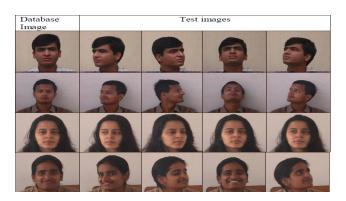

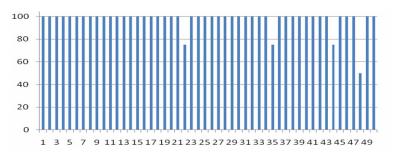

| Face Recognition Using Gray Level Weight Matrix (GLWM)<br>R.S. Sabeenian, M.E. Paramasivam, and P.M. Dinesh                         | 69 |

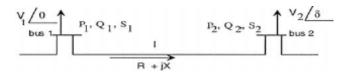

| <ul> <li>Location for Stability Enhancement in Power Systems Based on Voltage</li> <li>Stability Analysis and Contingency Ranking</li> <li>C. Subramani, S.S. Dash, M. Arunbhaskar,</li> <li>M. Jagadeeshkumar, and S. Harish Kiran</li> </ul> | 73  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Reliable Barrier-Free Services (RBS) for Heterogeneous Next<br>Generation Network<br>B. Chandra Mohan and R. Baskaran                                                                                                                          | 79  |

| Poster Paper                                                                                                                                                                                                                                   |     |

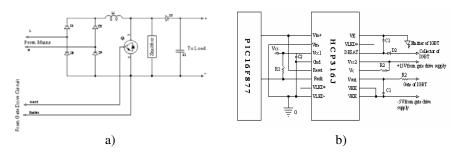

| Power Factor Correction Based on RISC Controller<br>Pradeep Kumar, P.R. Sharma, and Ashok Kumar                                                                                                                                                | 83  |

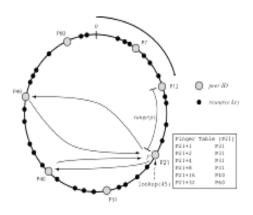

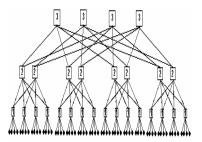

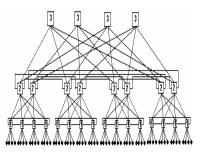

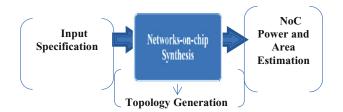

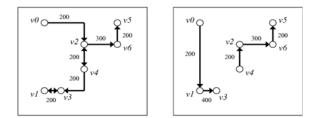

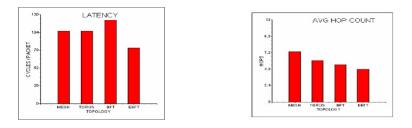

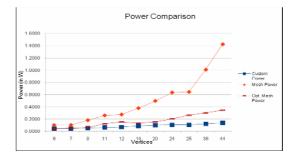

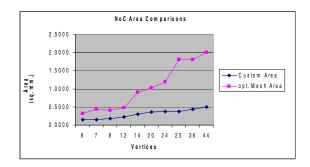

| Customized NoC Topologies Construction for High Performance<br>Communication Architectures<br><i>P. Ezhumalai and A. Chilambuchelvan</i>                                                                                                       | 88  |

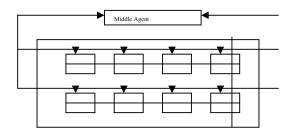

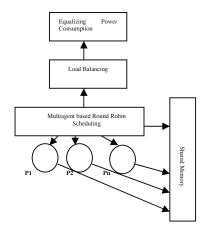

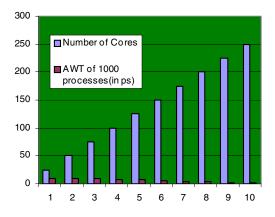

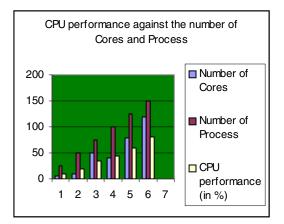

| Improving CPU Performance and Equalizing Power Consumption forMulticore Processors in Agent Based Process SchedulingG. Muneeswari and K.L. Shunmuganathan                                                                                      | 95  |

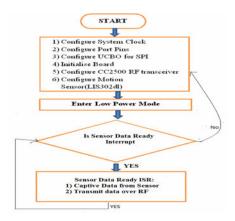

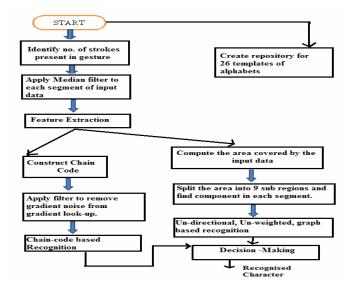

| Wireless 3-D Gesture and Chaaracter Recognition<br>Gaytri Gupta and Rahul Kumar Verma                                                                                                                                                          | 105 |

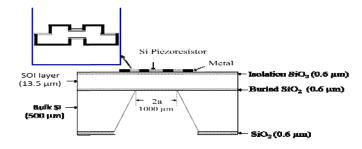

| Design of High Sensitivity SOI Piezoresistive MEMS Pressure Sensor<br>T. Pravin Raj, S.B. Burje, and R. Joseph Daniel                                                                                                                          | 109 |

| Power Factor Correction in Wound Rotor Induction Motor Drive By<br>Using Dynamic Capacitor<br>G. Venkataratnam, K. Ramakrishna Prasad, and S. Raghavendra                                                                                      | 113 |

| An Intelligent Intrusion Detection System for Mobile Ad- Hoc Networks<br>Using Classification Techniques<br>S. Ganapathy, P. Yogesh, and A. Kannan                                                                                             | 117 |

| Author Index                                                                                                                                                                                                                                   | 123 |

## Bandwidth Enhancement of Stacked Microstrip Antennas Using Hexagonal Shape Multi-resonators

Tapan Mandal<sup>1</sup> and Santanu  $Das^2$

<sup>1</sup> Department of Information Technology, Government College of Engineering and Textile Technology, Serampore, Hooghly, India tapanmandal20@rediffmail.com <sup>2</sup> Department of Electronics & Tele-Communication Engineering, Bengal Engineering and Science University, Shibpur, Howrah, India santanumdas@yahoo.com

**Abstract.** In this paper, wideband multilayer stacked resonators, combination of planner patches and stacked with defected ground plane in normal and inverted configuration are proposed and studied. Impedance and radiation characteristics are presented and discussed. From the results, it has been observed that the impedance bandwidth, defined by 10 dB return loss, can reach an operating bandwidth of 746 MHz with an average center operating frequency 2001 MHz, which is about 32 times that of conventional reference antenna. The gain of studied antenna is also observed with peak gain of about 9 dB.

**Keywords:** Stacked resonators, Regular hexagonal microstrip antenna, Broad band width, Defected ground plane.

#### **1** Introduction

Conventional Microstrip Antennas (MSA) in its simplest form consist of a radiating patch on the one side of a dielectric substrate and a ground plane on the other side. There are numerous advantages of MSA, such as its low profile, light weight, easy fabrication, and conformability to mounting hosts [1-4]. An MSA has low gain, narrow bandwidth, which is the major limiting factor for the widespread application of these antennas. Increasing the BW of MSA has been the major thrust of research in this field. Multilayer multiple resonators are used to increase the bandwidth [5-6]. Two or more patches on different layers of the dielectric substrates are stacked on each other. This method increases the overall height of the antenna but the size in the planer direction remains almost the same as the single patch antenna. When the resonance frequencies of two patches are close to each other, a broad bandwidth is obtained [7]. In this paper, simulation is carried out by method of moment based IE3D simulation software.

#### 2 Antenna Design and Observation

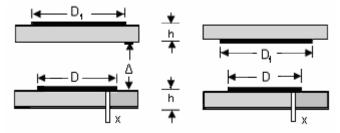

A two-layer stacked configuration of an electromagnetically coupled MSA (ECMSA) is shown in Fig.1. The bottom patch is fed with a co-axial line and the top parasitic

Fig. 1. Electro-magnetically coupled MSA (a) normal (b) inverted configurations with feed connection to bottom patch

patch is excited through electromagnetic coupling with the bottom patch. The patches can be fabricated on different substrates and an air gap can be introduced between these layers to increase the bandwidth. In the normal configuration the parasitic patch is on the upper side of the substrate shown in Figure 1(a). In the inverted configuration, as shown in Figure 1(b), the top patch is on the bottom side of the upper substrate [5-7] In this case, the top dielectric substrate acts as a protective layer from the environment.

Regular Hexagonal MSA (RHMSA), rather than circular MSA(CMSA), rectangular MSA or a square MSA, could also be stacked to obtain an enhanced broad BW.

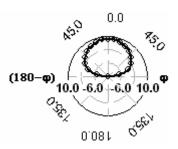

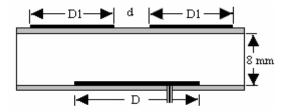

Now a two-layered stacked CMSA is designed on a low cost glass epoxy substrate having dielectric constant er = 4.4 and height of the substrate h = 1.59 mm. The diameter of bottom patch D = 36mm. The diameter of top patch is optimized so that its resonance frequency is close to that of the bottom patch and is found to be equal to D1=48 mm (1B1T) for air gap  $\Delta = 5.03$  fold of substrate thickness. The patch is fed at x = 16.5mm away from its center. The IB1T stacked circular MSA exhibits 384 MHz (17.9%) impedance bandwidth (BW) with center frequencies of 2.18 GHz and 2.47 GHz having return losses -17.76 dB and -17.5 dB. The peak gain (PG) and the average gain (AG) of the structure at frequency 2.32 GHz are 7.96dB and 1.63 dB for  $E_{\phi}$  at  $\phi=90^{0}$  plane. In the inverted configuration the air gap between the two stacked resonators is 6.03 fold of substrate thickness. The return losses -27dB and -12 dB respectively having impedance bandwidth (BW) 380 MHz (17%). The peak gain (PG) and the average gain (AG) of the structure at average frequency 2.32 GHz are 8.4 dB and 2.09 dB respectively for  $E_{\phi}$  at  $\phi=90^{0}$  plane.

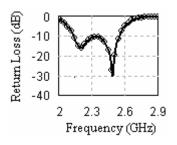

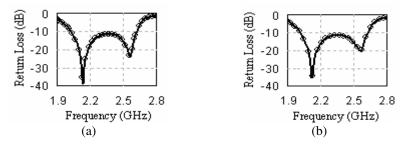

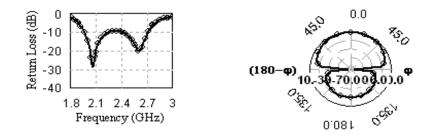

Now a two-layer stack RHMSA is designed for the operation in the frequency range 2.1 GHz – 2.5 GHz. All metallic patchs are designed on the same type of substrate as before. A RHMSA with diameter D = 39mm has been considered as a bottom patch of stacked microstrip antenna. The diameter of top patch is optimized so that its resonant frequency is close to that of the bottom patch and the diameter is found to be equal to D1 =52mm. The air gap between two substrate layers is ( $\Delta$ ) 8mm. The bottom layer patch is probe fed along the positive x -axis at X=16.5 mm away from the center. The return loss characteristic of 1B1T configurations is shown in Fig. 2(a), yields 453MHz (19.7%) impedance bandwidth with at center frequency of 2.1 GHz and 2.48 GHz having return losses (S<sub>11</sub>) -15.19dB and -29 dB respectively. The PG and AG of the structure at 2.48 GHz are 8.7 dB and 2.4 dB respectively for E $\phi$  at  $\phi$ = 90<sup>0</sup> plane as shown in Fig. 2(b). Now impedance BW and AG have been improved by 69 MHz and 0.8 dB respectively from 1B1T configuration of CMSA.

in normal configuration

Fig. 2(a). Return loss characteristic of 1BIT Fig. 2(b). Radiation pattern characteristic of 1B1T in normal configuration

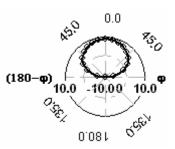

Fig. 3(a). Return loss characteristic of 1B1T in inverted configuration

Fig. 3(b). Radiation pattern characteristic of 1B1T in inverted configuration

In inverted configuration, the air gap between two stacked substrate is  $\Delta = 9$ mm. Here air gap has been increased by 1mm from the normal configuration to keep the same distance between the metallic patch in Z-direction. The return loss characteristic is shown in Fig. 3(a) and it exhibits that center frequencies are 2.2 GHz and 2.5GHz with return loss -25.98 dB and -13.50dB having BW 405 MHz (18.43%). The PG and the AG of the structure is 8.4 dB and 2.08 dB at frequency 2.35 GHz for E $\varphi$  at  $\varphi = 0^0$ plane shown in Fig 3. (b). Now BW has been enhanced by 25 MHz from inverted 1B1T configuration of CMSA.

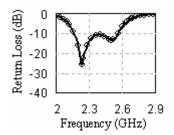

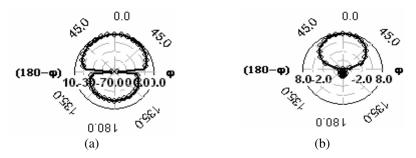

Now four identical circular slots are embedded in the antenna ground plane of glass epoxy substrate, aligned with equal spacing and parallel to the patch radiating edges of the 1B1T stack resonators of RHMSA in normal configuration. The radius of each circular slot is 8 mm and all are placed 14.14 mm away from the center of the patch. The embedded slots in the ground plane have very small effects on the feed position for achieving good impedance matching. The return loss characteristic is shown in Fig. 4(a) and it exhibits 618MHz (26.4%) impedance BW with center frequencies at 2.14 GHz and 2.56 GHz having return losses -37.96dB and -23.82 dB respectively. The peak gain and the average gain of the structure at frequency 2.34 GHz are 8.15 dB and 1.89dB respectively for E $\phi$  at  $\phi = 90^{\circ}$  plane as shown in Fig. 5 (a). Increasing of bandwidth probably is associated with the embedded slots in the ground plane. It is also noted that backward radiation of the antenna is increased compared to the reference antenna. This increase in the backward radiation is contributed by embedded slots in the ground plane. But in inverted configuration with defected

Fig. 4. Meandered ground plane return loss characteristics of (a) normal (b) inverted configuration of 1B1T

Fig. 5. Meandered ground plane radiation pattern characteristics of (a) normal (b) inverted configuration of 1B1T

ground plane having 617 MHz (26.48%) impedance bandwidth with center frequency 2.12 GHz and 2.55 GHz return losses -34.8 dB and -20.0dB as shown in Fig. 4 (b). The peak gain and average gain of the structure at resonant frequency 2.12 GHz are 8.27 dB and 2.11dB respectively for E $\phi$  at  $\phi = 90^{\circ}$  plane as shown in Fig. 5 (b). Here it is observed that BW has been enhanced from the without defected ground plane of 1B1T stack resonators but AG is decreased.

The BW of antenna increases when multi-resonators are coupled in planner or stacked configuration. In this work, a single RHMSA with D = 39 mm is considered at the bottom layer with coaxial feed and another two patch with D1 = 48 mm is placed at the top layer (1B2T) shown in Fig. 6. The metallic patches each is made on the same substrate ( $\varepsilon_r$  = 4.4 and h = 1.59mm) as before. Air gap between two stacked substrate is 8mm. The gap between two planner parasitic patches at the top layer is 6mm.

Fig. 6. Proposed two- layer 1B2T stacked configuration

Fig. 7(a). Meandered ground plane return loss Fig. 7(b). Meandered ground plane radiation characteristic of 1B2T pattern of 1B2T

Return loss characteristic of 1B2T configuration exhibits 505MHz (20%) impedance BW with center frequency 2.46 GHz having return loss –30 dB. The peak gain and the average gain of the structure at frequency 2.46GHz is 9.85 dB and 3.55dB respectively for  $E_{\phi}$  at  $\phi = 90^{\circ}$  plane. Therefore this structure increases the AG by 1.58dB due to the increased area.

Here the ground plane of 1B2T stack resonator is defected by four identical circular slots with diameter 16mm, all are placed symmetrically in the ground plane. Gap between the circular slots is 4mm. The distance between center of circular slots and center of the bottom patch is 14.14mm. The return loss characteristic exhibits impedance bandwidth 764 MHz (33%) with center frequencies are 2.06GHz and 2.6GHz having return losses -27.6dB and -19.8 dB respectively shown in Fig. 7(a). At frequency 2.3GHz, the peck gain and the average gain of the structure is 8.77dB and 2.54dB at  $E_{\phi}$ ,  $\phi$ =90<sup>0</sup> shown in Fig. 7 (b).

The analyzed antenna is presented in Fig. 6. The upper patches are fed electromagnetically by the bottom patch through a coupling area, and whose size determines the coupling magnitude. According to the transmission line theory, the open circuits realized by the radiating edges of the driven patch are located underneath the low impedance planes of the upper patches. Hence, the fringing fields are attracted, so that high electromagnetic coupling is achieved and therefore a large bandwidth may be obtained. A narrow spacing between the upper patches moves the radiating edges of the lower patch closer to the transversal axes of the upper patches associated with the short circuit planes, and therefore increases the coupling. One must ensure that the resonance modes of the two upper patches are excited in phase. This is the obviously the case for two identical patches are arranged symmetrically with respect to the longitudinal axis of the lower patch, in the H-plane. This is also true for the gaps coupled parasitic two patches displayed symmetrically in the E plane. They are placed in similar impedance planes, so that a same type coupling occurs between the bottom patch and each of the upper patches. Since the resonance frequencies are close, the phase of the current densities is constant over the whole patch. The induced currents from the lower patch to the upper patches are also in phase.

#### 3 Conclusion

Gap-coupled planar multi-resonator and stacked configurations are combined to obtain wide bandwidth with higher gain. In this paper, simulation details results have been presented for coaxial probe, two layers stacked resonator, combination of planar and stacked resonators MSA, and ground plane defected stacked MSA. Simulation results exhibit gradual improvement of impedance BW and AG from 453 MHz to 764 MHz and 1.63dB to 2.54dB respectively with nominal frequency variation.

This type MSA is offering grater bandwidth and higher gain over circular, square, triangular and rectangular Structure. It is less expensive due to less area of the metallic patch over conventional structure. Therefore this structure is most significant for broadband operation.

Acknowledgement. This work is supported by AICTE, New Delhi.

#### References

- 1. Kumar, G., Ray, K.P.: Broad Band Microstrip Antennas. Artech House, Norwood (2003)

- Splitt, G., Davidovitz, M.: Guideline for the Design of Electromagnetically Coupled Microstrip Patch Antennas on two layersubstrate. IEEE Trans. Antennas Propagation AP-38(7), 1136–1140 (1990)

- Sabban, A.: A new broadband stacked two layer microstrip antenna. In: IEEE AP –S Int. Sump. Digest, pp. 63–66 (June 1983)

- Damiano, J.P., Bennegueouche, J., Papiernik, A.: Study of Multilayer Antenna with Radiating Element of Various Geometry. Proc. IEE, Microwaves, Antenna Propagation, Pt. H 137(3), 163–170 (1990)

- 5. Wong, K.L.: Design of Nonplanar Microstrip Antenna and Transmission Lines. Wiley, New York (1999)

- Legay, H., Shafai, L.: New Stacked Microstrip Antenna with Large Bandwidth and high gain. IEE Pros. Microwaves, Antenna Propagation, Pt. H 141(3), 199–204 (1994)

- BalaKrishan, B., Kumar, G.: Wideband and high gain broad band Electromagnetically coupled Microstrip Antenna. IEEE Trans. AP-S Int. Symp. Digest, pp. 1112–1115 (June 1998)

- Legay, H., Shafai, L.: A New Stacked Microstrip Antenna with Large Bandwidth and high gain. IEE Pros. Microwaves, Antenna Propagation, 949–951 (1993)

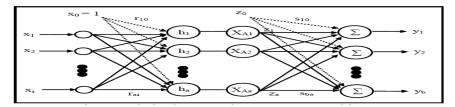

## Study of Probabilistic Neural Network and Feed Forward Back Propogation Neural Network for Identification of Characters in License Plate

Kemal Koche<sup>1</sup>, Vijay Patil<sup>2</sup>, and Kiran Chaudhari<sup>2</sup>

<sup>1</sup> Computer Science and Engineering, Nagpur Uni, India kemalkoche@yahoo.com <sup>2</sup> Computer Science and Engineering, Pune Uni, India vijay\_bpatil@yahoo.co.in, kiran\_chaudhari@rediffmail.com

**Abstract.** The task of vehicle identification can be solved by vehicle license plate recognition. It can be used in many applications such as entrance admission, security, parking control, airport or harbor cargo control, road traffic control, speed control and so on. Different Neural Network for character identification like Probabilistic Neural Network and Feed-Forward Back-propagation Neural Network has been used and compared. This paper proposes the use of Sobel operator to identify the edges in the image and to extract the License plate. After extraction of license plate the characters are isolated and passed to character identification system. The method used to identify characters are Probabilistic Neural Network with 108 neurons which gives accuracy of 91.32%, Probabilistic Neural Network with 35 neurons which gives accuracy of 96.73% and Feed Forward Back Propagation Neural Network which gives accuracy of 96.73%.

**Keywords:** License Plate Recognition (LPR), Intelligent Transportation System (ITS), Probabilistic Neural Network (PNN), Optical Character Recognition (OCR).

#### **1** Introduction

During the past few years, intelligent transportation systems (ITSs) have had a wide impact in the life of people, as their scope is to improve transportation safety and mobility and to enhance productivity through the use of advanced technologies. ITSs systems are divided into intelligent infrastructure systems and intelligent vehicle systems [1]. In this paper, a computer vision and character recognition algorithm for the license plate recognition (LPR) had being presented to use as a core for intelligent infrastructure like electronic payment systems at toll or at parking and arterial management systems for traffic surveillance. Moreover, as increased security awareness has made the need for vehicle based authentication technologies extremely significant, the proposed system may be employed as access control system for monitoring of unauthorized vehicles entering private areas. The license plate remains as the principal vehicle identifier despite the fact that it can be deliberately altered in fraud situations or replaced (e.g., with a stolen plate). Therefore, ITSs rely heavily on robust LPR systems. The focus of this proposed system is on the integration of a novel segmentation technique implemented in an LPR system able to cope with outdoor conditions if parameterized properly.

#### 2 Literature Survey

Recognition algorithms reported in previous research are generally composed of several processing steps, such as extraction of a license plate region, segmentation of characters from the plate, and recognition of each character. Papers that follow this three-step framework are covered according to their major contribution in this section.

#### 2.1 License Plate Detection

As far as extraction of the plate region is concerned; there are several techniques for identification of license plates. The technique based on Sliding window method [1] [7] shows good results. The method is developed in order to describe the "local" irregularity in the image using image statistics such as standard deviation and mean value. Techniques based upon combinations of edge statistics and mathematical morphology featured very good results [2]. In these methods, gradient magnitude and their local variance in an image are computed. The paper [3] explains the license plate detection based on color features and mathematical morphology. Since these methods are generally color based, they fail at detecting various license plates with varying colors. The paper [5] proposes a novel license plate localization algorithm for automatic license plate recognition (LPR) systems. The proposed approach uses color edge information to refine the edge points extracted in a gray-level image. In [8], the paper presents a hybrid license plate location method based on characteristics of characters' connection and projection. This method uses edge detection technique and binarization method.

#### 2.2 Character Segmentation

Number of techniques, to segment each character after localizing the plate in the image has also been developed, such as feature vector extraction and mathematical morphology [1] [2]. An algorithm based on the histogram, automatically detects fragments and merges these fragments before segmenting the fragmented characters. A morphological thickening algorithm automatically locates reference lines for separating the overlapped characters. The paper uses binarization method, proposed by Sauvola [1][8], to obtain binary image. We have used adaptive thresholding method in our LPR system.

#### 2.3 Character Recognition

For the recognition of segmented characters, numerous algorithms exploited mainly in optical character-recognition applications, Neural networks [1] [2] [8], Hausdorff distance [9] measures the extent to which each point of a model set lies near some point of an image set and vice versa. Support vector machines (SVM)-based character

recognizer [10] can be used to provide acceptable alternative for recognition of characters in License plate. Multilayer Perceptron Neural Networks can be use for license plate character identification. The training method for this kind of network is the error back -propagation (BP). The network has to be trained for many training cycles in order to reach a good performance. This process is rather time consuming, since it is not certain that the network will learn the training sample successfully. Moreover, the number of hidden layers as well as the respective neurons has to be defined after a trial and error procedure. Probabilistic Neural Networks (PNNs) for LPR are explained in [1]. Hausdorff distance has all the mathematical properties of a metric. Its main problem is the computational burden. Its recognition rate is very similar to that obtained with Neural-Network classifiers, but it is slower. Therefore, it is good as a complementary method if real-time requirements are not very strict. A suitable technique for the recognition of single font and fixed size characters is the pattern matching technique [7]. Although this one is preferably utilized with binary images, properly built templates also obtained very good results for grey level images. A similar application is described in [7], where the authors used a normalized cross correlation operator. We have compared and studied Probabilistic Neural Network, Feed Forward Back Propagation Neural Network in this paper.

#### **3** Proposed Method

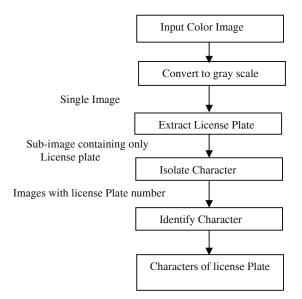

The proposed system focuses on the design of algorithm used for extracting the license plate from a single image, isolating the characters of the plate and identifying the individual characters. Our license plate recognition system can be roughly broken down into the following block diagram in fig. 1.

Fig. 1. Flow chart of basic LPR system

The system takes color image as input and converts it into gray scale image. The system then extracts the license plate from the image. The extracted license plate is then segmented to obtain sub-images containing license plate characters, which are then passed to OCR machine which will then identify the characters. The extraction and isolation of License plate had been done using segmentation techniques and character recognition had been done using different neural networks i.e. Probabilistic Neural Network and Feed-Forward Back-Propagation Neural Network.

#### 4 Liscence Plate Recognition (LPR) System

We can divide the algorithm into three parts, first where the License plate is extracted from the input RGB image and second, where extracted License plate is segmented down to individual images containing the character in the License plate. In the last part the segmented characters are then identified using different character identification methods.

#### 4.1 License Plate Extraction Machine

The purpose of this part is to extract the License Plate from a captured image. The output of this module is the gray picture of the LP precisely cropped from the captured image, and a binary image, which contains the normalized LP. The most important principle in this part is to use conservative algorithms which as we get further becomes less conservative in order to, step by step, get closer to the license plate, and avoid loosing information in it, i.e. cutting digits and so on. We have used Sobel operator to identify edges of the License plate.

#### 4.2 Character Segmentation

In order to segment the characters in the binary license plate image the method named peak-to-valley is used. The methods first segments the picture in digit images getting the two bounds of the each digit segment according to the statistical parameter DIGIT\_WIDTH = 18 and MIN\_AREA = 220. For that purpose, it uses a recursive function, which uses the graph of the sums of the columns in the LP binary image. This function parses over the graph from left to right, bottom-up, incrementing at each recursive step the height that is examined on the graph.

#### 4.3 OCR Engine

Given the digit image obtained at the precedent step, this digit is compared to digits images in a dataset, and using the well-known Neural Network method, after interpolations, approximations and decisions algorithm, the OCR machine outputs the closest digit in the dataset to the digit image which was entered. As known, neural network is a function from vector to vector, and consists of an interpolation to a desired function. Matlab provides very easy-to-use tools for Neural Networks, which permits to concentrate on the digit images dataset only. We have compared two neural networks namely Probabilistic Neural network and Feed-Forward back propagation neural network; Results are given in the table 1.

Table 1. Comparison of LPR system for different Neural Networks OPNN-Original Probablistic Neural Network, IPNN-Inproved Probablistic Neural Network, FFBP-Feed Forward Back Propogation

|                       | OPNN<br>(108Neurons)                                                 | IPNN<br>(35Neurons)                                                  | FFBP                                                                 |

|-----------------------|----------------------------------------------------------------------|----------------------------------------------------------------------|----------------------------------------------------------------------|

| Problems<br>encounter | To identify similar<br>character like<br>'I'&1,'O'&0,'Z'&<br>7,'B'&8 | To identify similar<br>character like<br>'I'&1,'O'&0,'Z'&<br>7,'B'&8 | To identify similar<br>character like<br>'I'&1,'O'&0,'Z'&<br>7,'B'&8 |

| Improvement           | Improved after<br>Training                                           | Improved after<br>Training                                           | Improved after<br>Training                                           |

| Accuracy              | 91.42%                                                               | 96.73%                                                               | 96.73%                                                               |

| Features              | Accurate , But<br>require large<br>memory.                           | More accurate<br>than OPNN                                           | Accurate and<br>require less<br>memory                               |

#### 5 Conclusion

This method can be used to implement a real time application for identifying the vehicle. The license number can be compared with database or use to maintain information at parking lot or at entrance. This paper proposes the use of Sobel operator to identify the edges in the image and to extract the License plate. We have done all the processing on gray scale image hence external colors and environmental conditions has least effect on the system. After extraction of license plate the characters are isolated and passed to character identification system.

The method used to identify characters Probabilistic Neural Network with 108 neurons which gives accuracy of 91.32%, Probabilistic Neural Network with 35 neurons which gives accuracy of 96.73% and Feed Forward Back Propagation Neural Network which gives accuracy of 96.73%.

#### References

- Anagnostopoulos, C., Anagnostopoulos, I., Tsekouras, G., Kouzas, G., Loumos, V., Kayafas, E.: Using sliding concentric windows for license plate segmentation and processing. IEEE Transactions on Intelligent Transportation Systems 7(3) (September 2006)

- Yang, F., Ma, Z.: Vehicle License Plate location Based on Histogramming and Mathematical Morphology. In: IEEE Workshop on Automatic Identification Advance Technology (October 2005)

- Syed, Y.A., Sarfraz, M.: Color Edge Enhancement based Fuzzy Segmentation of License Plates. In: Proceedings of the Ninth International Conference on Information Visualisation (IV 2005). IEEE, Los Alamitos (2005)

- Koval, V., Turchenko, V., Kochan, V., Sachenko, A., Markowsky, G.: Smart. License Plate Recognition System Based on Image Processing Using Neural Network. In: IEEE Workshop on Intelligent Data Acquisition and Advanced Computing Systems: Technology and Application, Lviv, Ukraine, pp. 8–10 (September 2003)

- Lin, C.-C., Huang, W.-H.: Locating License Plate Based on Edge Features of Intensity and Saturation Subimages. In: IEEE Second International Conference on Innovative Computing, Information and Control, September 5-7, p. 227 (2007)

- ter Brugge, M.H., Stevens, J.H., Nijhuis, J.A.G., Spaanenburg, L.: License Plate Recognition Using DTCNNs. In: Fifth IEEE Intenational Workshop on Cellular Neural Networks and their Applications, London, England, April 14-17 (1998)

- Anagnostopoulos, C., Alexandropoulos, T., Boutas, S., Loumos, V., Kayafas, E.: A template-guided approach to vehicle surveillance and access control. In: IEEE Conference on Advance Video and Signal Based Survillance, September 15-16, pp. 524–539 (2005)

- Zhang, C., Sun, G., Chen, D., Zhao, T.: A Rapid Locating Method of Vehicle License Plate Based on Characteristics of Characters' Connection and Projection. In: 2nd IEEE Conference on Industrial Electronics and Applications, May 23-25, pp. 2546–2549 (2007)

- 9. Huttenlocher, D.P., Klanderman, G.A., Rucklidge, W.J.: Comparing Images Using the Hausdorff Distance. IEEE Transactions on Pattern Analysis and Machine Intelligence 15(9), 850–863 (1993)

- Kim, K.K., Kim, K.I., Kim, J.B., Kim, H.J.: Learning-based approach for license plate recognition. In: Proceedings of the 2000 IEEE Signal Processing Society Workshop Neural Networks for Signal Processing, December 11-13, vol. 2, pp. 614–623 (2000)

## Efficient Minimization of Servo Lag Error in Adaptive Optics Using Data Stream Mining

Akondi Vyas<sup>1,2</sup>, M.B. Roopashree<sup>1</sup>, and B. Raghavendra Prasad<sup>1</sup>

<sup>1</sup> Indian Institute of Astrophysics, II Block, Koramangala, Bangalore 560034, India <sup>2</sup> Indian Institute of Science, Malleswaram, Bangalore 560012, India {vyas,roopashree,brp}@iiap.res.in

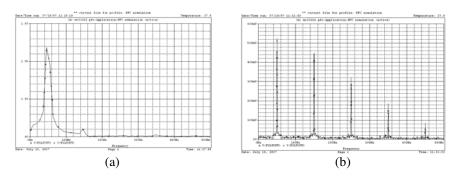

**Abstract.** Prediction of the wavefronts helps in reducing the servo lag error in adaptive optics caused by finite time delays (~ 1-5 ms) before wavefront correction. Piecewise linear segmentation based prediction is not suitable in cases where the turbulence statistics of the atmosphere are fluctuating. In this paper, we address this problem by real time control of the prediction parameters through the application of data stream mining on wavefront sensor data obtained in real-time. Numerical experiments suggest that pixel-wise prediction of phase screens and slope extrapolation techniques lead to similar improvement while modal prediction is sensitive to the number of moments used and can yield better results with optimum number of modes.

**Keywords:** Adaptive optics, data stream mining, turbulence prediction, servo lag error.

#### 1 Introduction

Data mining is a productive statistical analysis of large amounts of data to discover patterns and empirical laws which are not obvious when manually examined[1]. Astronomy has seen data mining as a tool to archive large amounts of data. Advances in experimental astronomy depends on designing larger telescopes. The need for increasing the size of ground based telescopes and disadvantages of space telescopes is well known. A fast real-time feedback loop based wavefront correcting technology called adaptive optics is used to correct the incoming wavefront distortions due to turbulent atmosphere. But there exist time lags (comparable to optimum closed loop bandwidth) because of the delay between the wavefront correcting instrument and the wavefront sensor. These delays are essentially due to the finite exposure time and non-zero response times of the instruments in the feedback loop. These errors can be minimized through progressive prediction of wavefronts using time series data mining. The prediction accuracy depends strongly on the atmospheric turbulence parameters which fluctuate in time. Hence, there is a need for continuous monitoring of the atmospheric turbulence parameters for optimum performance of adaptive optics systems. However, this requires highly sophisticated instruments and control. Here, we investigated this problem through numerical simulations by adaptively changing the prediction parameters using data stream mining of existing wavefront sensor data.

The need for prediction in adaptive optics is illustrated in the next section. The dependence of the parameters that control prediction process on atmospheric turbulence is described in section 3. The steps involved and the methods used in the prediction methodology are explained in section 4. The last section presents the results and conclusions.

#### **2** Need for Prediction in Adaptive Optics

Successful performance of the adaptive optics system needs operation at optimized bandwidth which is near the Greenwood frequency,  $f_G$  [2]. In the case of sites with good seeing, the minimum bandwidth requires running the closed loop faster than 200 Hz. It is a challenging task to run the closed loop system at the Greenwood frequency, due to the unavoidable time lags in the closed loop [3]. The minimum exposure time  $(\tau_{exp})$  required for reasonably accurate wavefront sensing limits the rate of closed loop operation. Added to this delay is the response timescales of the controller  $(\tau_c)$  and corrector  $(\tau_{dm})$ . Hence the total servo lag is  $\tau_L = \tau_{exp} + \tau_c + \tau_{dm}$ . The existence of servo lag implies that the sensed wavefront is corrected after a delay  $\tau_L$ . From the spatial and temporal correlation of wavefronts, it is possible to track the evolution of wavefronts and hence greatly reduce the effect of the servo lag. Various predictors are suggested in the literature<sup>[4]</sup> which assume Taylor's frozen in turbulence approximation, also verified experimentally[5]. Under this approximation, for a telescope of diameter, D (say, D=2m), the decorrelation time is  $\tau_d = D / v_a$  ( $\tau_d = 200$ ms at  $v_a = 10$  m/s). Two wavefronts separated in time by larger than  $\tau_d$  are said to be decorrelated.

The wavefront prediction parameters can either be the local wavefront slopes measured by a sensor or the wavefront modes formed from an orthogonal basis. There are two important extrapolation parameters that decide the prediction accuracy. One of them is the number of wavefronts (n) to be used for optimum prediction and the other is the time representing the best predictable future ( $\tau_{pf}$ ). The parameters n and  $\tau_{pf}$  are called the data stream parameters and obviously depend on  $\tau_d$  and the spatial coherence length represented by Fried parameter,  $r_0$ . The existence of fluctuations in  $r_0$  and the wind speed that controls  $\tau_d$  are well known. These variations also drive n and  $\tau_{pf}$  into instability hence causing "Concept Drift". Analyzing the reported  $r_0$  measurements at the Oukaimeden site, it can be observed that within 0.5 hrs,  $r_0$  fluctuates with a standard deviation of 1.33 cm[6]. The RMS variability of wind velocity is 0.5 m/s within 10 s as was reported[7, 8]. The temporal variability of the turbulence parameters are also site dependent[9]. Temporal data mining methods help in predicting the future turbulence phase screens[10].

#### **3** Prediction Accuracy and Data Stream Mining

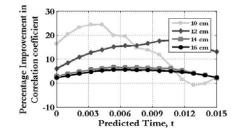

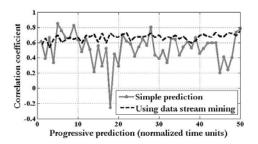

To test the dependence of prediction accuracy on the way optimum data stream parameters change with time, Monte Carlo simulations of closed loop adaptive optics system were performed within the decorrelation timescales of atmospheric turbulence. For the simulation of atmosphere like phase screen following Kolmogorov statistics, Zernike moments were computed through the covariance relation derived by Noll[11]. In order to closely depict temporal turbulence, the angular rate of the wind,  $\omega$  and  $v_a$ the wind velocity are included in the simulations[12]. In order to understand the dependence of wavefront prediction accuracy on the data stream parameters, simulations were performed with fluctuating wind speed  $v_a$  and Fried's parameter,  $r_0$ . As shown in Fig. 1, the wavefront prediction accuracy strongly depends on the best predictable phase screen. The percentage improvement in the correlation, PI<sub>CC</sub> plotted in the y-axis of the graph is calculated using the formula,

$$PI_{CC} = \frac{X_{Pre-Act} - X_{Last-Act}}{X_{Last-Act}} \times 100$$

(1)

where,  $X_{Last-Act}$  is the correlation coefficient between the last phase screen in the training data cube and the actual phase screen which is to be predicted,  $X_{Pre-Act}$  represents the correlation coefficient of the predicted phase screen and the actual phase screen.

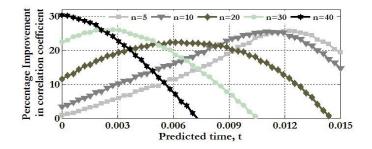

Fig. 1. Case: n = 5; Optimum  $\tau_{pf}$  depends on  $r_0$  (values given in legend) and  $\tau_d$

The choice of optimum segment size,  $n_{opt}$  ( $\tau_{pf}$  given) can be made by studying PI<sub>CC</sub> at different 'n' values as shown in Fig. 2. For the phase screens generated to obtain these curves, the decorrelation time was set to 20 ms. For n = 5, the percentage improvement in correlation is maximum at t = 12 ms and for n = 30, the percentage improvement in correlation is maximum at t = 3 ms. Considering a servo lag error of 5 ms, optimum value of 'n' is found to be in the range from 20 to 30. Also, the minimum improvement is above 20% and below 30% within the decorrelation time. If this training were not present, using n = 5 for the case of 5 ms time lag would lead to a prediction which is ~10% less accurate.

**Fig. 2.** Choosing optimum 'n' through knowledge of  $\tau_{pf}$

#### 4 Prediction Methodology

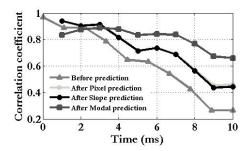

Data cube is a three dimensional data grid which piles up the phase screens in the order of their arrival in time. To avoid memory constraints and taking the advantage of the fact that the atmospheric parameters slowly change in time, the volume of the data cube is kept constant by removing the oldest phase screen on the addition of a latest one. The major steps involved in the prediction process include (a) data stream parameter estimation and data selection (b) Prediction through extrapolation. Optimum number of phase screens is selected for extrapolation from the data cube as discussed in the earlier section. There exists many methods for segmentation of the time series in the literature[1]. The top-down, bottom-up and sliding windows methods were discussed previously in the case of adaptive optics using modal and zonal predictors[10]. Linear as well as nonlinear extrapolation methods can be applied for prediction of future phase screens. If the data is well trained in the manner suggested previously, linear predictor would be the best choice. In any case, nonlinear methods are not very well known to give better results. Linear extrapolation requires to fit the evolution of 'nopt' latest phase screens with appropriate straight lines and extrapolate them to obtain the required phase screen after a time,  $\tau_{pf}$ . In the case of zonal prediction, either the individual pixels of the phase screens (computationally tedious, accurate) or the local slopes of a Shack Hartmann sensor (SHS) (faster, less accurate) are used for extrapolation into the future. In the case of modal prediction, Zernike coefficients (or modes corresponding to any orthogonal basis) are extrapolated. Modal prediction performs better than the slope extrapolation method (Fig. 4).

#### 5 Results and Conclusions

Monte Carlo simulations were performed on phase screens simulated which include the fluctuations in the data stream parameters in time. A comparison of a simple prediction methodology and data stream mining based prediction is shown in Fig. 3. Pixel-wise linear predictor is a lossless predictor, although computationally challenging, where the computational time involved increases linearly with the number of elements (pixels in this case) to be predicted (400 elements takes 1.25s; computations done on 1.4GHz Intel(R) Core(TM)2 Solo CPU with 2GB RAM). Slope extrapolation is a prediction methodology where the information that is available is the local slopes measured via a SHS. Hence, the number of elements to be predicted in this case is  $2 \times A_{SH}$ , where  $A_{SH}$  is equal to the number of subapertures of the Shack Hartmann sensor used for wavefront sensing. A factor of '2' appears due to the existence of 'x' and 'y' slopes. Increasing the number of apertures of a SH sensor would increase the computational time in this case.

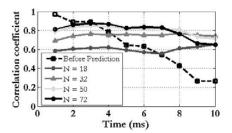

Modal prediction is yet another prediction methodology where the number of elements is determined by the number of orthogonal modes (N) to be used to represent the phase screen reasonably accurately. Individual phase screens are decomposed into complex Zernike polynomials through fast computation of Zernike moments and these moments are used for prediction and wavefront analysis[13].

A comparison of the performance of these methods is shown in Fig. 4. It can be observed that the performance of the pixel-wise prediction overlaps with the slope

Fig. 3. Comparison of a simple prediction against data stream mining based prediction. Data stream mining guides us to a better and more stable prediction performance (variance reduced  $\sim$ 17 times).

Fig. 4. A comparison of prediction methodologies

Fig. 5. Performance of Modal prediction at different 'N'

extrapolation method. Modal prediction using N=72, gives better results when compared with slope extrapolation with 100 subapertures and pixel-wise prediction having to extrapolate for 10,000 pixels. Using a smaller value of 'N' would largely deteriorate the prediction accuracy as can be seen in Fig. 5. It is also interesting to note that for a servo lag in the range 7-10 ms, the prediction is better with N=50 than with N=72. Hence a more intelligent algorithm is required in modal prediction case wherein 'N' can also be closely examined akin to other data stream parameters. In conclusion, it is possible to efficiently and consistently predict wavefronts in adaptive optics using real-time data stream mining of sensor data through modal and zonal methods through a continuous training of the data stream parameters.

#### References

- 1. Last, M., Kandel, A., Bunke, H.: Data mining in time series databases. World Scientific, Singapore (2004)

- Greenwood, D.P.: Bandwidth specification for adaptive optics systems. J. Opt. Soc. Am. 67, 390–393 (1977)

- Lloyd-Hart, M., McGuire, P.: Spatio-temporal prediction for adaptive optics wavefront reconstructors. In: ESO Astrophysics Symposia (1996)

- 4. Poyneer, L., Veran, J.P.: Predictive wavefront control for adaptive optics with arbitrary control loop delays. J. Opt. Soc. Am. 25, 1486–1496 (2008)

- Poyneer, L., Dam, M.V., Veran, J.P.: Experimental verification of the frozen flow atmospheric turbulence assumption with use of astronomical adaptive optics telemetry. J. Opt. Soc. Am. A 26, 833–846 (2009)

- Benkhaldoun, Z., Abahamid, A., El Azhari, Y., Lazrek, M.: Optical seeing monitoring at the Oukaïmeden in the Moroccan high atlas mountains: first statistics. Astronomy and Astrophysics 441, 839–843 (2005)

- Els, S.G., Travouillon, T., Schock, M., Riddle, R., Skidmore, W., Seguel, J., Bustos, E., Walker, D.: Thirty Meter Telescope Site Testing VI: Turbulence Profiles. PASP 121(879), 527–543 (2009)

- Benkhaldoun, Z.: Oukaimeden as a potential observatory: Site testing results. In: Proceedings of the ASP Conference, vol. 266, p. 414 (2002)

- Travouillon, T., et al.: Temporal variability of the seeing of TMT sites. In: Stepp, L.M., Gilmozzi, R. (eds.) SPIE, vol. 7012(1), pp. 701–220 (2008)

- Vyas, A., Roopashree, M.B., Prasad, B.R.: Progressive Prediction of Turbulence Using Wave-Front Sensor Data in Adaptive Optics Using Data Mining. IJTES 1(3) (2010)

- 11. Noll, R.J.: Zernike polynomials and atmospheric turbulence. J. Opt. Soc. Am. 66, 207–211 (1976)

- Hu, L., Xuan, L., Cao, Z., Mu, Q., Li, D., Liu, Y.: A liquid crystal atmospheric turbulence simulator. Opt. Express 14, 11911–11918 (2006)

- Hosny, K.M.: Fast computation of accurate Zernike moments. Journal of Real-Time Image Processing 3, 97 (2008)

## Soft Switching of Modified Half Bridge Fly-Back Converter

Jini Jacob<sup>1</sup> and V. Sathyanagakumar<sup>2</sup>

<sup>1</sup> Senior Lecturer, Dept. of Electrical and Electronics Engineering, MVJ College of Engineering, Bangalore jinijacobp@yahoo.com

<sup>2</sup> Professor and Chairman, Dept. of Electrical Engineering, University Visvesvaraya College of Engineering, Bangalore vsnk@yahoo.com

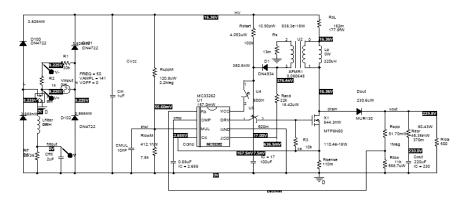

**Abstract.** This paper presents soft switching of modified half bridge fly-back converter. The power switches in this converter are turned on at ZVS and the rectifier diode is turned on and off at ZCS. The auxiliary switch is turned off at ZCS. The voltage stress across the switch is equal to the supply voltage and soft switching is achieved for all the switching devices. Compared to half bridge fly-back converter, this modified circuit has improved efficiency. A 5V/2A prototype is implemented to verify the practical results.

Keywords: Half Bridge, Fly-back, soft switching, ZVS, ZCS.

#### 1 Introduction

The conventional fly-back converter is widely being used for low power applications due to its low cost and robust characteristics. But the hard switching operation and high switching stresses across the switching devices introduced a lot of limitation in the application of fly-back converter. A number of topologies have been introduced recently to overcome these drawbacks. Among the different topologies, the active clamp converter [1] reduces the switching losses but the voltage stress across the power switch is same as that of conventional fly-back converter.

The asymmetrical fly-back topologies [2-3] can achieve zero voltage switching operation of the power switches but the hard switching of the output rectifier at turn off increases the energy loss due to reverse recovery current. In half bridge fly-back converter [4], the switches are turned on at zero voltage and the output diodes are turned on and off at zero current. The main disadvantage of the circuit is that the efficiency is not improved because of switching losses during turn off though the switches are turned on at zero voltage and output diodes are turned on and off at zero current. In this topology the input current drawn from the supply at light load condition is more and it is also another reason for low efficiency.

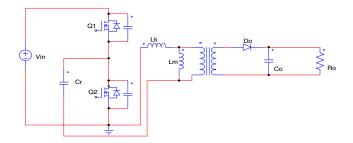

In this proposed topology as shown in Fig. 1, a modified half bridge fly-back converter without any output inductor in which the power switches are turned on at zero voltage and turned off at zero current and the rectifier diode is turned on and off at zero current which reduces the switching losses. The voltage stress across the power switches are clamped at supply voltage. The switching frequency is selected to be slightly more than resonant frequency which depends on the leakage inductance of the transformer and the resonant capacitor.

The operational principles, design considerations and simulation and practical results are given in this paper. Testing of 5V/2A prototype confirms that the experimental results are similar to the simulation results.

#### 2 **Operational Principles**

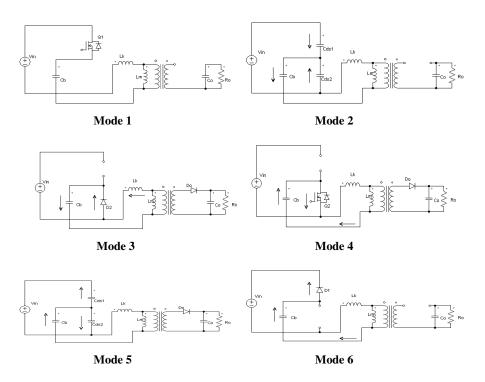

In the proposed simplified circuit, resonant inductor is the sum of leakage inductance of the transformer and the stray inductances and is shown external to the transformer in the Fig.1. The leakage inductance is very small compared to the magnetising inductance of the transformer. The operation of this converter can be explained by considering six operating modes in a switching cycle. The equivalent circuit in each mode is as shown in Fig. 2.

Fig. 1. Circuit Diagram of the Modified Half Bridge Fly-back Converter

#### **2.1** Mode 1 $(t_0 - t_1)$

At  $t=t_0$ ,  $Q_1$  is turned on and  $Q_2$  is off. The output diode is reverse biased and the capacitor  $C_o$  supplies to load  $R_o$ .  $C_b$ ,  $L_m$  and  $L_k$  forms a series resonant circuit with the voltage source in series. The voltage source charges the resonant capacitor and the current through  $L_m$  and  $L_k$  increases linearly. The equivalent circuit for mode 1 operation is shown in Fig. 2. The governing circuit equations are given by,

$$(L_m + L_k)\frac{di_{L_k}}{dt} + v_c = V_{in}.$$

(1)

$$C_b \frac{dV_c}{dt} = i_{L_k} = i_{L_m} .$$

#### **2.2** Mode 2 $(t_1 - t_2)$

This mode starts when  $Q_1$  is turned off and  $Q_2$  is also off.  $C_{ds1}$ ,  $C_b$ ,  $L_m$  and  $L_k$  forms a series resonant circuit.  $C_{ds1}$  charges and  $C_{ds2}$  discharges. The equivalent

circuit for this mode is shown in Fig. 2. When  $C_{ds2}$  completely discharges the body diode of  $Q_2$  starts conducting and mode 3 starts. The governing equations for this mode are given by

$$(L_m + L_k)\frac{dt_{L_k}}{dt} = -V_{in} + v_c + V_{ds1}$$

(3)

$$C_b \frac{dV_c}{dt} = i_{L_k} = i_{L_m} \tag{4}$$

#### **2.3** Mode 3 $(t_2 - t_3)$

Both  $Q_1$  and  $Q_2$  are off in this mode. The body diode of  $Q_2$  starts conducting. This mode ends when  $Q_2$  is turned on at zero voltage. The output diode starts conducting. The circuit governing equations are given by,

$$(L_m + L_k)\frac{di_{L_k}}{dt} = v_c + V_{fd}$$

<sup>(5)</sup>

$$C_b \frac{dV_c}{dt} = i_{L_k} = i_{L_m} \tag{6}$$

#### **2.4** Mode 4 $(t_3 - t_4)$

In this mode  $Q_1$  is off and  $Q_2$  is turned on at zero voltage switching. Output diode is conducting and the transformer secondary voltage is reflected to primary side of the transformer.  $C_b$  discharges through  $L_m$  and  $L_k$ . The circuit governing equations are,

$$L_k \frac{di_{L_k}}{dt} = v_c - L_m \frac{di_{L_m}}{dt}$$

(7)

$$C_b \frac{dV_c}{dt} = i_{L_k} \tag{8}$$

$$i_{D_o} = n(i_{L_k} - i_{L_m})$$

(9)

Fig. 2. Equivalent Circuit in different Modes of Operation

#### **2.5** Mode 5 $(t_4 - t_5)$

At  $t=t_4$ ,  $Q_2$  is turned off.  $C_{ds2}$  charges and  $C_{ds1}$  discharges. When completely discharges, the body diode of  $Q_1$  starts conducting and this mode ends. The equivalent circuit for this mode is shown in Fig. 2. The output diode is turned off at ZCS at the end of this mode. The circuit governing equations for this mode are given by,

$$(L_m + L_k)\frac{di_{L_k}}{dt} = \mathbf{v}_{\rm c} - \mathbf{V}_{\rm ds2} \tag{10}$$

$$C_b \frac{dV_c}{dt} = -i_{L_k} = -i_{L_m} \tag{11}$$

$$C_{ds2}\frac{dV_{ds2}}{dt} = \frac{1}{2}i_{L_k} = \frac{1}{2}i_{L_m}$$

(12)

#### **2.6** Mode 6 $(t_5 - t_6)$

This mode starts when  $C_{ds1}$  discharges and body diode of  $Q_1$  starts conducting. The output diode is reverse biased and  $C_a$  supplies the load. This mode ends when  $Q_1$  is

turned on again at ZVS in the next cycle. The equivalent circuit for this mode is shown in Fig. 2. The governing circuit equations are given by,

$$(L_m + L_k)\frac{di_{L_k}}{dt} = -V_{\rm in} + v_{\rm c} - V_{\rm fd}$$

(13)

$$C_b \frac{dV_c}{dt} = -i_{L_k} = -i_{L_m} \tag{14}$$

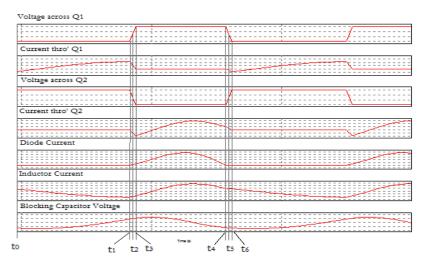

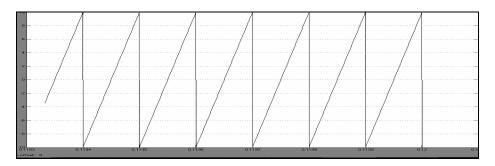

The theoretical waveforms in each mode are as shown in Fig. 3.

Fig. 3. Theoretical Waveforms showing Modes of Operation

#### **3** Simulation and Experimental Results

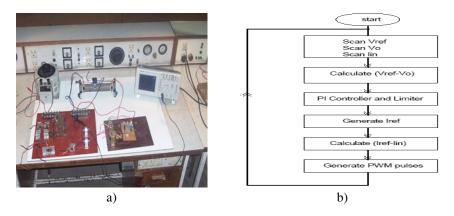

The modified half bridge fly-back converter is simulated using Powersim software and the simulation results are shown in Fig. 5 - Fig. 6. The prototype of the proposed modified half bridge fly-back converter is constructed for the specifications as given below.

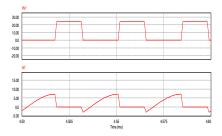

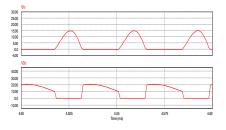

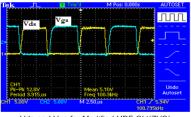

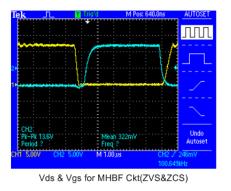

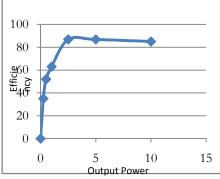

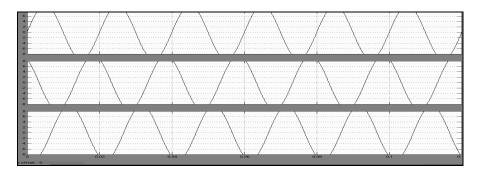

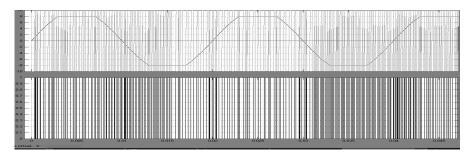

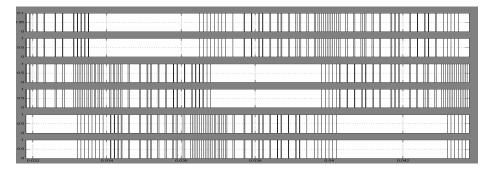

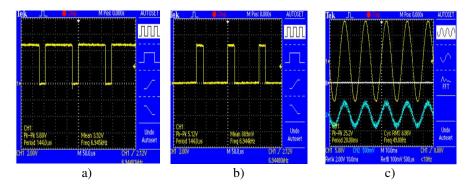

Input voltage  $V_{in}$ : 20V-30V; Output voltage  $V_o$ : 5V; Output current  $I_o$ : 2A; Switching Frequency  $f_s$ : 100kHz ;Resonant capacitor  $C_b$ : 2.2µF; Magnetizing inductance : 27µH; Leakage inductance:3µH. The prototype is tested for its operational feasibility and ZVS and ZCS operations. Fig. 4a. shows the voltage across switch1 and current through it. Fig. 4b. shows the voltage across switch2 and current through it. Fig. 5. shows the current through the output diode and voltage across it. From the simulation results as shown in Figs. 4 and 5, it is clear that the switches are turned on at ZVS and turned off at ZCS. The output diode is turned on and off at ZCS. The waveforms obtained from the practical results are as shown in Figs. 6 and 7, which are closely matching with the simulation results. The peak to peak capacitor voltage is nearly half of the supply voltage. The switching losses are reduced and the efficiency is improved compared to half bridge fly-back converter. The output verses efficiency curve shown in Fig. 8 shows that a maximum efficiency of 90% is achieved which is around 10% higher than the half bridge fly back topology. The advantage of this circuit is that the efficiency is high even at larger output power ratings of the converter since the percentage of fixed losses will be reduced. Therefore this circuit can be used for high power applications.

30.00 20.00 10.00 0.0 1000 7.50 5.00 2.50 -2.50 -5.00 -7.50 4.50 4.55 Time (ms

Fig. 4a. Voltage and Current Waveforms of Switch 1

-10.00

Fig. 4b. Voltage and Current Waveforms of Switch 2

Vds and Vgs for Modified HBF Ckt(ZVS)

Fig. 5. Diode current and voltage waveforms Fig. 6. V<sub>gs</sub> & V<sub>ds</sub> Waveforms of switch 1

Fig. 7. V<sub>gs</sub> & V<sub>ds</sub> Waveforms of switch 2

Fig. 8. Output power Vs Efficiency Curve

#### 4 Conclusion

In this work, a new modified half bridge fly-back converter with ZVS and ZCS operation is proposed, analysed, designed and implemented in which the drawbacks of half bridge fly-back converter are eliminated. In this proposed converter, the power switches are turned on at zero voltage and turned off at zero current. The output rectifier diode is turned on and off at zero current. The operation of this converter is analysed considering six modes. A 10W prototype is designed for a switching frequency of 100 kHz. It is found that the practical waveforms closely resemble the simulation waveform. Excellent line and load regulation is achieved and the ripple is found to be less than 0.5%. Maximum efficiency at rated input voltage is found to be nearly 90%.

#### References

- Aqik, A., Cadirci, I.: Active clamped ZVS forward converter with soft-switched synchronous rectifier for high efficiency, low output voltage applications. IEEE Proc. Electr. Power Appl. 150(2) (March 2003)

- 2. Gu, Y., Lu, Z.: A Novel ZVS Resonant Reset Dual Switch Forward DC-DC Converter. IEEE Transactions on Power Electronics 22(1) ( January 2007)

- Watson, R., Lee, F.C., Hua, G.C.: Utilization of an Active-Clamp Circuit to Achieve Soft Switching in Fly back Converters. IEEE Trans. on Power Electronics 11(1), 162–169 (1996)

- 4. Wu, L.-M., Pong, C.-Y.: A Half Bridge Fly back Converter with ZVS and ZCS Operations. In: 7th International Conference on Power Electronics (October 2007)

## A Novel Approach for Prevention of SQL Injection Attacks Using Cryptography and Access Control Policies

K. Selvamani<sup>1</sup> and A. Kannan<sup>2</sup>

<sup>1</sup> Department of Computer Science & Engineering <sup>2</sup> Department of Information Science & Technology, Anna University, Chennai - 600025, TamilNadu, India {Selvamani, kannan}@annauniv.edu

Abstract. In this era of social and technological development, SQL injection attacks are one of the major securities in Web applications. They allow attackers to obtain an unrestricted and easy access to the databases to gain valuable information. Although many researchers have proposed various effective and useful methods to address the SQL injection problems, all the proposed approaches either fail to address the broader scope of the problem or have limitations that prevent their use and adoption or cannot be applied to some crucial scenarios. In this paper we propose a global solution to the SQL injection attacks by providing strong encryption techniques and policy based access control mechanism on the application information. We initially encrypt the message using an encryption engine in the server before we store the values into the database with Policy-based Access Control, data is stored in the encrypted form and while accessing it again we decrypt them and provide the data for the user in a secured manner with the control of policy based access.

Keywords: Encryption, Decryption, String Transform, Access Control.

#### 1 Introduction

SQL injection is a web application attack in which malicious code is inserted into strings that are passed to an instance of SQL Server for parsing and execution. Any procedure that builds SQL statements should be reviewed for injection vulnerabilities because SQL Server will execute all syntactically valid queries that it receives. Due this reason even parameterized data can be manipulated manually who is aware of the SQL injection code and by the determined attacker. The primary way of SQL injection consists of direct insertion of malicious code into user-input variables that are concatenated with SQL commands which are executed. Another form of attack is direct attack that injects malicious code into strings that are destined for storage in a table or as metadata in the database. When the stored strings are next concatenated into a dynamic SQL command, the malicious code is executed.

Hence this injection process works by terminating a text string that is appended to a new command. Since, the inserted command may have additional strings appended to it before it is executed. Therefore, the malefactor terminates the injected string with a comment mark "--". Subsequent text is ignored at execution time. A characteristic or the most diagnostic or the disastrous feature of such an SQL Injection Attack (SQLIA) is that they change the intended and inherent structure of queries issued. By usefully exploiting these vulnerabilities and pitfalls, an attacker can issue his own SQL commands directly to the database and can manipulate the database in his own intended way, thereby gaining what he want from the attacked system. These attacks are serious threat to the existing web applications and any web application that receives input from users and incorporates it into SQL queries to an underlying database.

In this paper we propose a new approach for dynamic detection and prevention of SQL injection attacks. Intuitively, our approach works by encrypting the message (typically field values) and stored in the database with Access control policy. The general mechanism that we use to implement this approach is based on dynamic encryption, which encrypts certain data in a program at runtime. This is done using the Encryption Engine.

In this system, access control can choose to update privilege levels of the web request to control malicious requests. This process involves characterising the incoming requests using fuzzy rules and then generating updating messages and finally updating the access privilege levels to reflect the level of users. In this three access levels namely privilege user lever, application programmer level and naïve user level are used. Queries with privilege user and application programmer level are sent to the web database with normal encryption, where as the queries with naïve user levels are sent through policy levels and then to the web database.

If the encrypted data is being queried again, the encrypted stored values are again decrypted and it is returned as a response to the request in user understandable form with the help of access control mechanism. This is done using the decryption engine. This has several advantages such as the attacker should find the encryption key in order to find the encrypted data.

For example, Here we introduce a sample SQLIA [1] and discuss the methods that are already in use to prevent these. Consider a jsp example which uses the input from user (username, password) to retrieve the information about the account. The query would be

```

SELECT details FROM usertable WHERE username = ` + username + ` ' and password = ` ' + userpassword + ` ';

```

The JSP snippet for the same would be

```

String usern = getParameter ("username");

String userp = getParameter ("userpass");

String query = SELECT details FROM usertable WHERE username = `

+ usern + ` AND password = ` + userp + ` ;

Statement stmt = connetion.createStatement ();

ResultSet rs = stmt.executeQuery(query);

```

If the user input for username is hanuman

```

hanuman' – –

```

and password field is left empty, the query would be

query = SELECT details FROM usertable WHERE username = `hanuman - -'

and password = ` ';

thus the password comparison part of the query would be skipped since it is now in the comment section (the part after).

The remainder of this paper is organized as follows: Section 2 presents the related works in the field of SQL injection attacks and the existing systems. Section 3 depicts the proposed system architecture. Section 4 presents details of encryption and decryption techniques and its experimental setup. Section 5 provides the results of the implemented system in this paper. Section 6 gives a brief conclusion on this work and suggests some possible future works.

#### 2 Related Works

There are many works in the literature that discuss about SQL Injection attacks. AM-NESIA [1] is a model- based technique that combines static analysis with runtime monitoring which is dynamic. Even though their system combines both static and dynamic technique but it fails in preventing new types of SQL attacks.

In another work, the authors [2] proposed Positive tainting and negative tainting, that has conceptual difference with that of the traditional tainting. Positive tainting is based on the identification, marking, and tracking of trusted, rather than untrusted data. In the case of negative tainting, incompleteness may lead to trusting data that should not be trusted and, ultimately leads to false negatives.

Another author Sruthi Bandhakavi [3] tries to solve this by discovering intent dynamically and then comparing the structure of the identified query after user input with the discovered intent. This works fine for normal queries but this approach fails when the external function is not protected. The SQL-IDS system [4] presented a technique which is composed of an anomaly detection system that uses abstract payload execution [6] and payload sifting techniques to identify web requests that might contain attacks that exploit memory violations.

A new method for protecting web databases [8] that is based on fine-grained access control mechanism was proposed by Alex Roichman and Ehud Gudes. This method uses the databases' built-in access control mechanisms enhanced with Parameterized Views and adapts them to work with web applications.

Another method proposed by Wissam Mallouli and Jean-Marie Orset [9] was a framework to specify security policies and test their implementation on a system. Their framework makes it possible to generate in an automatic manner, test sequences, in order to validate the conformance of a security policy.

In order to address this problem, this paper aims in providing global solutions to the SQL injection attacks by applying cryptography techniques and policy based access control mechanism together to prevent intelligently the SQL Injection attacks. We initially encrypt the message using an encryption engine in the server before we store the values into the database, data is stored in the encrypted form and while accessing it again we decrypt them and provide the results.

## **3** System Architecture

In this work, our intention is to detect SQL attack intelligently in a sneaky way. We encrypt the data as soon as we receive it from the user, even before we start processing anything from the user.

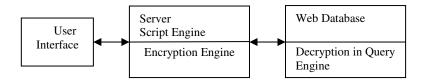

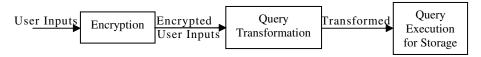

The proposed system architecture for encryption in server and decryption at web database is shown in figure 1. It contains the two components: Server along with encryption engine and the database with decryption engine. The encryption is carried over on the data at the server side, and the database before performing any query operation using the decryption engine decrypts the data.

Fig. 1. System Architecture

Figure 2 shows the encryption mechanism of the data at server side. The received user inputs are encrypted using the encryption mechanism and the encrypted data are transformed using the query transformation and finally the transformed data stored using query execution. The DES algorithm is used for the encryption of the data at the server side. DES encrypts and decrypts data in 64-bit blocks, using a 64-bit key (although the effective key strength is only 56 bits, as explained below). It takes a 64-bit block of plaintext as input and outputs a 64-bit block of cipher text. Since it always operates on blocks of equal size and it uses both permutations and substitutions in the algorithm, DES is both a block cipher and a product cipher.

DES has 16 rounds, meaning the main algorithm is repeated 16 times to produce the cipher text. It has been found that the number of rounds is exponentially proportional to the amount of time required to find a key using a brute-force attack. So as the number of rounds increases, the security of the algorithm increases exponentially.

#### 3.1 Key Scheduling

Although the input key for DES is 64 bits long, the actual key used by DES is only 56 bits in length. The least significant (right-most) bit in each byte is a parity bit, and should be set so that there are always an odd number of 1s in every byte. These parity bits are ignored, so only the seven most significant bits of each byte are used, resulting in a key length of 56 bits.

Fig. 2. Encryption mechanism at the server side

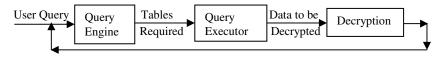

Figure 3 shows how the database querying engine has to be modified, hence it can be used for both encryption and decryption. Providing the encrypted data will give the actual user input, from which the required processing is done at the server. Each time the database has to operate on some value stored in the database, it performs Algorithm 1.

Fig. 3. Encryption mechanism at the database

Consider the query string

```

String query = SELECT details FROM useraccount WHERE

username = ` + username + ` ` and password = ` ` + password + ` `;

```

If user input for username is xxxx and password is yyyy then the username and password before being inserted is transformed to some other form. (i.e, encrypted) so that the actual SQL intend is not executed.

```

SELECT details FROM useraccount WHERE username =`mxsyz' and password = `sddxc';

```

From this we can identify the structure as SELECT, FROM, WHERE, AND.

Here we must also take care of the comments as the user input like the following may maintain the intent structure without comment but would fail if comment also is considered. If user input for username is hanuman and 1=1 then the query becomes as shown below. The structure without considering the comment would be same as the structure identified before SELECT, FROM, WHERE, AND.

SELECT details FROM useraccount WHERE username =`hanuman' and 1=1--' and password =`';

But now we are encrypting the entire data, we don't have to worry about the comments, even the comments are encoded to some other form, and thereby we miss the chance of an injection.

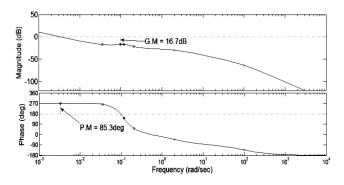

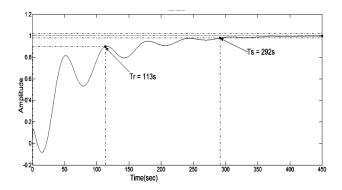

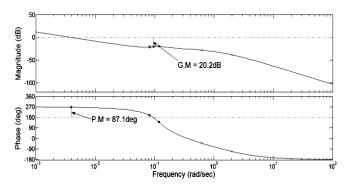

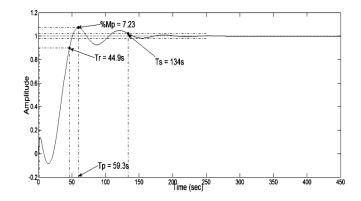

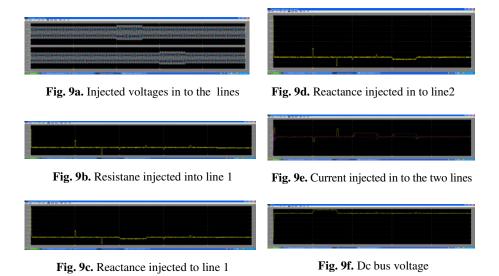

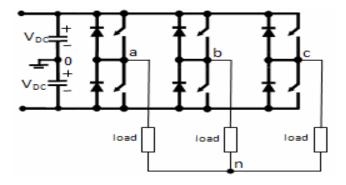

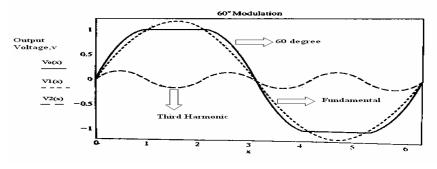

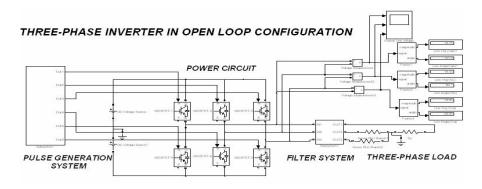

## 3.2 Deployment Requirements